#### **Emerging Nanoelectronics**

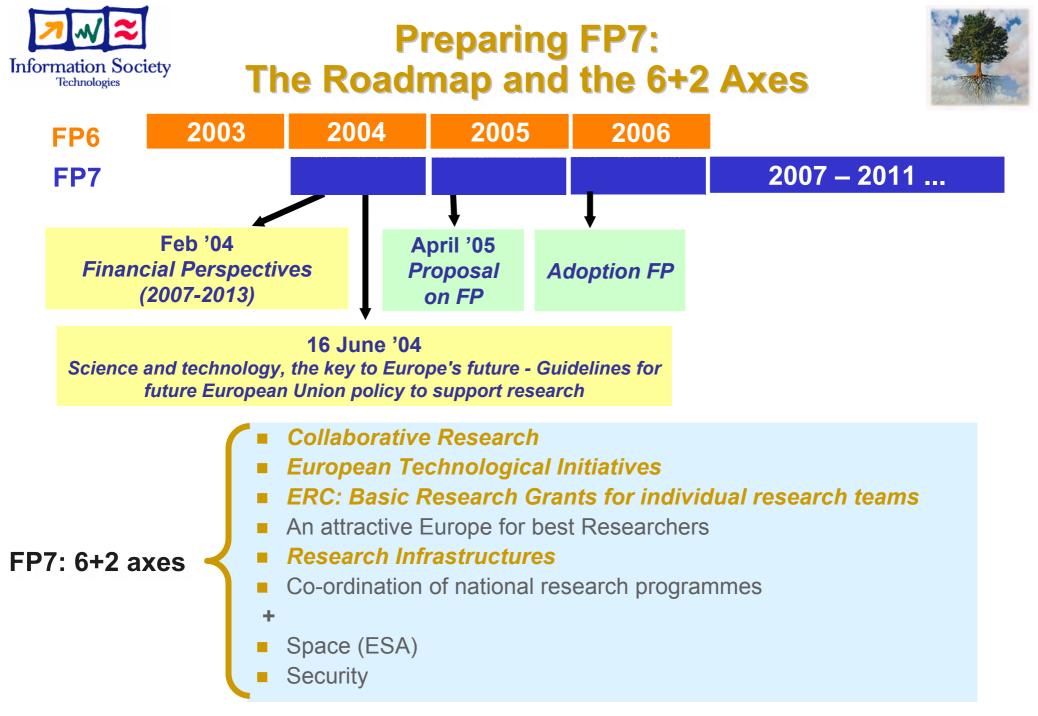

## **Preparing FP7**

1 February 2005

#### **Patrick Van Hove**

Future and Emerging Technologies DG Information Society & Media European Commission

## **Preparing FP7**

#### IST in FP7

- ERC & Basic Technology Research in ICTs  $\rightarrow$  Options Paper

- Collaborative RTD:

- ISTAG (Working Group on Grand Challenges)

- Strategic Orientations

- FP7 Workshops:

- > 21-22 Apr 04: FET FP7 Workshop

- > 12 Oct 04: ICT at the crossroads with Life Sciences

- > 8-9 Nov 04: Robotic Systems for extending Human Capabilities

- > 16 Dec 04: Emerging Nanoelectronics

- European Technology Platforms

- Developments of ENIAC platform

- Agenda 2020

#### Emerging Nanoelectronics: Preparing for FP7

#### Overall FP7 Workshop, Brussels, 21-22 April 2004

- Components

- Systems

- Intelligence

- Emerging Nanoelectronics Workshop, Brussels, 16 December 2004

- Draft Report now available: see <u>http://www.cordis.lu/ist/fet/nid.htm</u>

- PLEASE SEND US YOUR COMMENTS/INPUTS

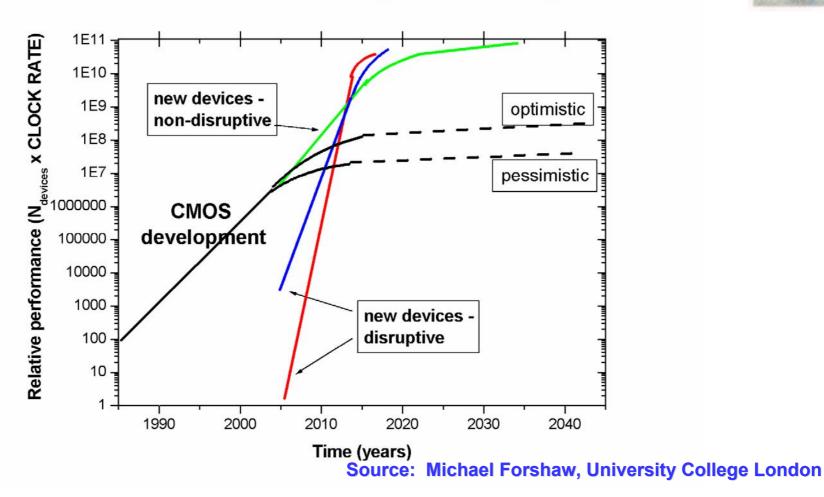

#### Why Emerging Nano R&D? 1. Limits of logic scaling

CMOS: Limits of scaling & limits of benefits of scaling: frequency increase, power scaling, delays, etc.

Non-conventional CMOS:

pursuing the shrinking until the "16 nm node" in 2019?

Charge-transport based emerging devices:

Nanotubes, Nanowires, Tunnelling devices, etc.

Breakthrough devices:

Quantum, spin-based, molecular, etc.

# **ERD: Logic: Limiting Factors**

Aim: Improve logic performance, density, cost, power

- Power dissipation density

- Tunnelling effects

- Discreteness of matter/dopants

- Limits of energy/device vs. thermal noise

- Beyond single devices: interconnections, etc.

- Patterning manufacturing accuracy

- Yield

- Etc.

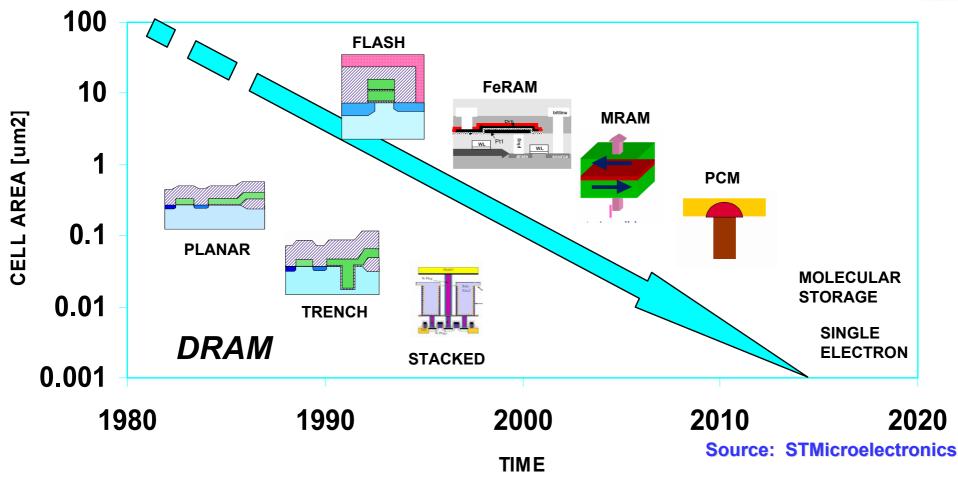

#### Why Emerging Nano R&D? 2. Limits of memory scaling

...and looking for solid-state non-volatile storage

## **ERD: Memories: Targets**

- Aim: Improve density, cost, retention time, write time & energy

- Limits to scaling of charge-based devices?

- More open to alternative approaches?

- In development: FRAM, MRAM, PCRAM

- New approaches: MIM, molecular, single/few e-, etc.

- Manufacturing issues

- Yield, Fault tolerance

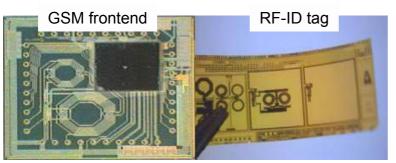

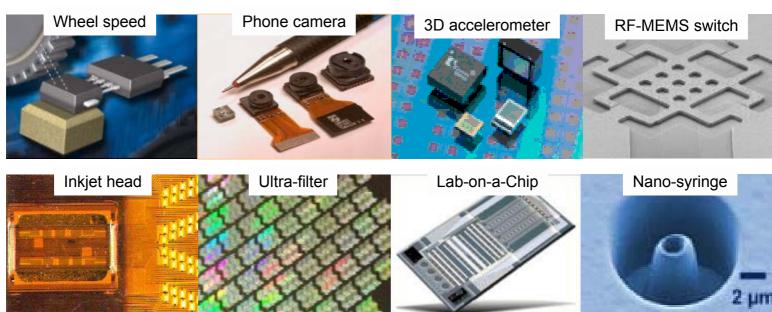

#### Why Emerging Nano R&D? 3. Value-added functions

sensors actuators

fluidics

**Source: Philips**

Intelligent Systems that compute and interact

### Towards a Research Programme: Topics

- Multidisciplinary Vision-driven Research

- Materials, Devices, Circuits, Architectures

- Experimental fabrication & characterisation

- Design Modelling

- Path towards mass-manufacturing~

- Curiosity-driven research

- Science and technology

- Not too many constraints

## Towards a Research Programme: Organisation

#### Collaborative Multidisciplinary Research

- Development of concepts

- Answering elementary limitations

- Patenting

- Curiosity-driven research

- New concepts Proof of concept

- Access to Infrastructure

- Needs to be managed & funded

- Expect to become specialised

- Roadmap: New impetus?

- Link with ENIAC

### Towards a Research Programme: Participants

- Majority expected from Academic and Research

- Role of industry

- Research participant

- Advise, assessment

- Mobility of researchers

- Among partners in projects

- "European single market" for researchers

- Synergy among various lines of action. Conference

- Integration of New Member States

- Better awareness of potential

- International Cooperation

Emerging Nanoelectronics: Preparing for FP7

Emerging Nanoelectronics Workshop, Brussels, 16 December 2004

Draft Report now available: see <u>http://www.cordis.lu/ist/fet/nid.htm</u>

PLEASE SEND US YOUR COMMENTS/INPUTS

**Additional Slides**

ITRS ERD Memory Devices

- Phase change memory

- Floating body DRAM

- Nano floating gate memory

- Single/few electron memory

- Insulator resistance change memory

- Molecular memories

ITRS ERD Logic devices

#### RSFQ

- Carbon Nanotubes

- Nanowire structures

- Crossbar structures

- Resonant tunnelling devices

- Single electron transistors

- Molecular devices

- Quantum cellular automata

- Spin transistors

ITRS ERD Architectures

- Quantum Cellular Automata Architecture

- Cellular nonlinear networks

- Fault-tolerant architectures

- Biologically-inspired architectures

- Coherent quantum computing

- Material synthesis

- Molecular synthesis

- Thin film synthesis

- Nanostructure synthesis

- Self and directed assembly

- Material interface, contacts

- Characterisation

- Characterisation of chemical, structural, impurity, defect, electronic information with nanometer or even atomic scale

- Characterisation of state properties

- Modelling and simulation