## NaPa KEYNOTES

## Emerging Nanopatterning Methods Based On MEMS Technology

Francesc Pérez-Murano, Juergen Brugger

1

Instituto de Microelectrónica de Barcelona, CNM-IMB, CSIC. Campus de la UAB. 08193-Bellaterra. SPAIN

Ecole Polytechnique Fédérale de Lausanne (EPFL). Microsystems Laboratory (LMIS)

Francesc.Pérez@cnm.es; juergen.brugger@epfl.ch

The development of nanosystems and nano-devices demands for patterning methods in the nanoscale. To bring them to the market, there is a need for fast, low-cost nanopatterning methods. In addition, an increased flexibility is important for the engineering of multi-material and multifunctional nano/micro-electro-mechanical systems (NEMS/MEMS), such as polymer-based electronic and sensor devices, 3D microfluidic systems, and bio-analytical systems. A series of alternative surface micro/nanopatterning methods based on MEMS technology are currently being developed, e.g. local fluidic dispensing [1] and shadow-mask deposition (nanostencil lithography) [2]. These methods rely on locally adding material onto the substrate without the need for resist layers, exposure and etch steps.

MEMS-based nanopatterning can be implemented in various manners: as scanning devices for the flexible, serial, writing of nanopatternings, as replication tools for the copying of an existing pattern, or as parallel scanning MEMS systems combining both, flexibility and increased aerial through-put. Figure 1 summarizes some existing methods that include MEMS tools.

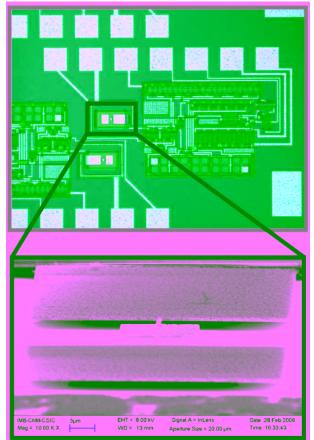

Nanostencil lithography is a resistless, single step patterning method based on direct, local deposition of material on an arbitrary surface through a solid-state membrane, e.g. a 200-nm thick silicon nitride (SiN) membrane. Although the method faces several challenges in terms of membrane fabrication at 100-nm scale, gap control, mechanical stability, aperture clogging, alignment for multi-layer patterning, etc. the technique has tremendous advantages for parallel processing. We have studied patterning by stencil lithography on various surfaces including CMOS chips. Figure 2 shows recent results of nanostencil for the patterning of CMOS wafer.

Dispensing of liquid at the nanometer scale has high interest for addressing local functionalization of surfaces and development of nanobiosensors and nanobiochips. Atomic force based technology can be used to locally deposit small quantity of liquid. MEMS technology can be used to fabricate arrays of silicon micro-levers with integrated read-out (piezoresistive) and fluidics systems, so that the deposition can be performed in a controllable and precise way. Two approaches are being developed: modfication of conventional AFM cantilevers and development of dedicated devices.

## **References:**

[1[ A. Meister et al., APL, 85(25), pp.6260-6262 (2004)

[2] M.A.F. van den Boogaart et al., Journal of Vacuum Science and Technology B, 22(6), pp. 3174-3177 (2004)

## **Figures:**

|                                                       | Molecule Delivery  | Thermo-mechanical         | Local Deposition            |

|-------------------------------------------------------|--------------------|---------------------------|-----------------------------|

|                                                       | We', soft-contact, | Nano-imprint, embossing,  | Stencil, vacuum, no contact |

|                                                       | 100 nm scale       | hard centact, 10 nm scale | 10-100 nm scale             |

| Single B.<br>Scanning<br>die novo                     | NADIS<br>BioPlume  | Heated AFM                | AFM<br>Nanostencil          |

| Parallel &                                            | Soft-              | NIL                       | Membrane                    |

| Static                                                | litho-             |                           | Nano-                       |

| Replication                                           | graphy             |                           | stencil                     |

| Parallel &<br>Scanning<br>Adaptive<br>mass-production | Parallet<br>DipPen | Millipede                 | Smart<br>Stencil            |

Figure 1: Compilation of nanopatterning method based on wet, dry and mechanical writing principles. The methods can be implemented either in scanning serial, static replication or dynamic parallel manner.

Figure 2. Nanostencil is used for parallel patterning of CMOS processed wafer with high resolution (200 nm). A full 4'' CMOS wafer is patterned, resulting in 1,872 functional nanomechanical resonators, each one monolithically integrated in a CMOS circuit