## **ELECTRON BEAM LITHOGRAPHY FOR THE FABRICATION OF NANO-SCALE FINFET DEVICE DEMONSTRATORS**

## J. Kretz, L. Dreeskornfeld, E. Landgraf, W. Rösner, W. Weber, and L. Risch Infineon Technologies Corporate Research, 81730 Munich, Germany E-Mail: johannes.kretz@infineon.com

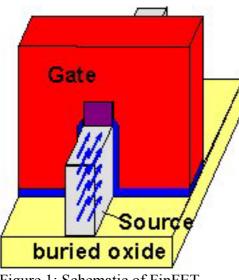

Multi-gate transistors are considered to be the ultimate device concept for use in future CMOS generations. The so-called FinFET [1] is a variant with a straightforward process flow [2]. A three-dimensional sketch of the FinFET can be seen in Fig.1. The small channels benefit from superior electrostatic channel control, resulting in enhanced turn-off behavior. However, its fabrication demands excellent lithography and etching techniques, since very small fins with smooth vertical sidewall surfaces, that define the channel region, have to be fabricated. Furthermore for the fabrication of a minimal device the overlay accuracy must be in the range of the fin width.

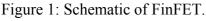

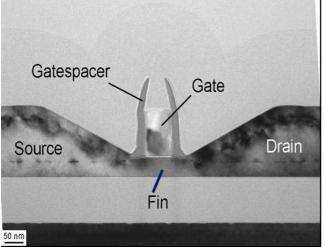

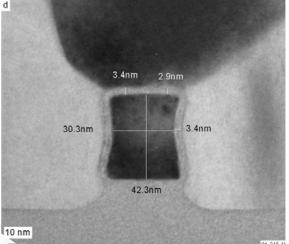

Electron beam lithography marks and optical alignment marks for all subsequent lithography steps are predefined with optical lithography on an SOI wafer with 50nm top silicon and etched into 100nm buried oxide. This topographic step yields sufficient secondary electron contrast of the alignment marks for an SEM based electron beam lithography at 10 keV with 100 nm thick calixarene resist [3]. The fin is exposed with electron doses around  $2mC/cm^2$ , pattern transfer is performed with high density plasma reactive ion etching into the hard mask stack of 20 nm Si<sub>3</sub>N<sub>4</sub> (only for the double gate) and 40 nm SiO<sub>2</sub> and - after resist removal into the mono-crystalline top silicon layer [4]. After removal of the etching passivation layer and thermal oxidation with 3 nm gate oxide, in-situ doped poly silicon is deposited with either phosphorous doping for the pMOS or boron doping for the nMOS transistor. A second ebeam lithographic step comparable to the one described above is accomplished with 10 nm overlay accuracy by in-situ scan-field correction on the 80 nm hard mask and 150 nm calixarene resist [5]. The gate is etched using a process similar to the fin etch and the source and drain regions are implanted (3.10<sup>15</sup> cm<sup>-2</sup> arsenic for n-channel, boron for p-channel, followed by a 1000°C anneal) prior to back-end processing. An SEM image of a test transistor is shown in figure 2. TEM cross-sections of a finished device (after back end processes) can be seen in figure 3 and figure 4.

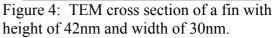

Figure 5 shows the output characteristics of typical FinFET devices with 25 nm (nMOS) and 20 nm (pMOS) fin width and gate lengths of 20 nm (nMOS) and 30 nm (pMOS). The width of the device is calculated using twice the fin height plus the fin width for current normalization. Maximum on-currents of  $1.6 \text{mA}/\mu\text{m}$  (nMOS) and  $0.6 \text{ mA}/\mu\text{m}$  (pMOS) can be achieved. The sub-threshold slopes reach typically values of 80 to 100 mV/dec. Low off-currents down to 3 pA/ $\mu$ m (nMOS) and 0.4 pA/ $\mu$ m (pMOS) have been achieved. The threshold voltages V<sub>t</sub> amount to 1.4 V for nMOS and 0.9 V for pMOS.

The first FinFETs with an excellent overlay accuracy of 10 nm allowing minimum transistor areas have been fabricated. By varying the application flow slightly either double-gate FinFETs or tri-gate FinFETs can be fabricated. The output characteristics show excellent on-currents. Hence, the FinFET is perfectly suited for CMOS applications at 45 nm and below. **References**

- [1] D. Hisamoto, W. Lee, J. Kedzierski, E. Anderson, H. Takeuchi, K. Asano, T. King, J. Bokor, C. Hu. Proc. IEDM 1998, p.1032

- [2] E. Landgraf, W. Rösner, R.J. Luyken. Proc. ESSDERC 2001, p.271

- [3] J. Kretz, L. Dreeskornfeld. Microel. Eng. 61-62, p.607 (2002)

- [4] L. Dreeskornfeld, J. Hartwich, J. Kretz, L. Risch, W. Rösner, D. Schmitt-Landsiedel. J. Vac. Sci. Technol. B 20(6), p.2777 (2002).

- [5] J. Kretz, L. Dreeskornfeld, J. Hartwich, W. Rösner. Microel. Eng. 67-68, p.763 (2003).

Figures

Figure 2: SEM of a FinFET test structure with connecting pads.

Figure 3: TEM cross section of a FinFET through source-drain.

Figure 5: Output characteristics of a p-channel (left) FinFET (width of fin: 20nm, height: 50nm, gate length: 30nm) and an n-channel (right) FinFET (width of fin: 25nm, height 50nm, gate length: 20nm).