# E-NANO NEWSLETTER

June 2005 Issue 1 http://www.phantomsnet.net

## **REPORT: RANS**

**Status of Research into Architectures for Nanoelectronic Systems**

15th NID Press Release and Working Groups

GDR-E GDR on Science and Applications of Nanotubes (NanoE)

## World's First Encyclopedia ever Published in Nanotechnology

See A-Z List of 410+ Articles at: www.aspbs.com/enn

# Encyclopedia of Nanoscience and Nanotechnology®

**10-Volume Set** (Available Both in Print & Online Editions) January 2004, ca. **10,000 pages**, Hardcover, ISBN: 1-58883-001-2, US\$6,992.00

#### Edited by Hari Singh Nalwa

*Editor-in-Chief,* Journal of Nanoscience and Nanotechnology (www.aspbs.com/jnn) Foreword by **Professor Richard E. Smalley, Nobel Prize Laureate**

**Encyclopedia of Nanoscience and Nanotechnology**<sup>®</sup> is the World's first encyclopedia ever published in the field of nanotechnology. The 10-volume Encyclopedia is an unprecedented single reference source that provides ideal introduction and overview of all aspects of nanoscale science and technology dealing with materials synthesis, processing, fabrication, probes, spectroscopy, physical properties, electronics, optics, mechanics, biotechnology, devices, etc. The Encyclopedia covers all fundamental and applied aspects of nanotechnology spanning from science to engineering to medicine. It is the only scientific work of its kind since the beginning of the field of nanotechnology bringing together core knowledge and the very latest advances.

#### **KEY FEATURES:**

- World's first and only encyclopedia ever published in the field of nanoscience and nanotechnology

- Most up-to-date reference work drawing on the past two decades of pioneering research

- Over 400 review chapters (ca. 10,000 pages) contributed by over 800 of the world's leading scientists

- Approximately 70,000 bibliographic citations providing extensive cross-referencing in each article

- About 6,800 figures, 650 tables, and hundreds of chemical structures and equations

- State-of-the-art review chapters of approximately 10 to 100 encyclopedia pages in length

- Edited and written by internationally known authoritative experts familiar with current technologies

- Truly international: authors from 35 countries

- Published in both print and online formats allowing multiple users and fully searchable text

**READERSHIP:** The encyclopedia is intended for a very broad audience working in the fields of nanotechnology and nanoscience having strong connections with materials science, electrical and electronic engineering, solid-state physics, surface science, aerosol technology, chemistry, colloid science, ceramic and chemical engineering, polymer science and engineering, sol-gel science, supramolecular science, mechanical engineering, metallurgy and powder technology, optical science and engineering, device engineering, aerospace engineering, computer technology, information technology, environmental engineering, biology, pharmacy, biotechnology, food science, etc.

"This encyclopedia is an indispensable source for any research professional as well as for technology investors and developers seeking up-to-date information on the nanotechnology among a wide range of disciplines from science to engineering to medicine. It should inspire future generations of academic and industrial researchers who endeavor to develop new nanoscale materials and devices." **Professor Richard E. Smalley, Nobel Prize Laureate**

"In view of the great interest that Nanoscience and Nanotechnology are attracting, the rapid development they are experiencing and of the profound impact they will have, an Encyclopedia covering this field is most welcome. It should become a source of inspiration as well as of information for a very wide range of scientists."

Professor Jean-Marie Lehn, Nobel Prize Laureate

Encyclopedia of SENSORS

## AMERICAN SCIENTIFIC PUBLISHERS

25650 North Lewis Way, Stevenson Ranch, California 91381-1439, USA Phone: (661) 254-0807 Fax: (661) 254-1207 Email: order@aspbs.com

ORDER Nanotechnology Books at: www.aspbs.com

www.phantomsnet.net

www.aspbs.com/eos

| Editorial Information                                                                                                                    | 4  |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| REPORT: RANS                                                                                                                             | 5  |

| The Status of Research into Architectures for Nanoelectronic Systems (RANS)<br>M. Forshaw and R. Stadler (University College London, UK) |    |

| 15th NID: PRESS RELEASE                                                                                                                  | 15 |

| 15th NID: M2e WG                                                                                                                         | 16 |

| Working Group on Mono-Molecular Electronics                                                                                              |    |

| 15th NID: NEMS WG                                                                                                                        | 17 |

| Working Group on Nano-Electro-Mechanical Systems                                                                                         |    |

| Nanonews                                                                                                                                 | 20 |

| Nano Conferences in Europe                                                                                                               | 22 |

| NanoVacancies                                                                                                                            | 23 |

| FP6 / FP7 Resources                                                                                                                      | 24 |

| TNT2005 Trends in Nanotechnology                                                                                                         | 25 |

| GDR-E                                                                                                                                    | 26 |

| GDR on Science and Applications of Nanotubes (NanoE)                                                                                     |    |

#### **EDITORIAL**

#### **Dear Readers**,

Welcome to the first issue of the "E-NANO Newsletter" that will threemonthly provide scientific articles, reports and updated information on Nanotechnology and more specifically Emerging Nanoelectronics.

Networking is vital to any scientist and even more so for persons working in the inter-disciplinary field of Nanotechnology. To fulfill this necessity, the "E-NANO Newsletter", edited by the PHANTOMS Foundation (nonprofit organisation based in Madrid, Spain) will provide comprehensive and updated information on latest advances in Emerging Nanotechnologies. In this way, this initiative achieves the aim of both raising the awareness of scientists in Nanotechnology and aiding them in developing beneficial collaborations and employment opportunities.

This newsletter will also publish relevant information about Integrated Projects funded by the European Commission such as NaPa (Emerging Nanopatterning Methods -NMP) aiming at developing new technologies such as nanoimprint or soft lithography and **Pico-Inside** (IST/FET/NID) that will explore Atomic Scale Technology with the final goal of integrating a complex logic gate inside a single molecule.

A selected range of emerging R&D activities such as Molecular Electronics is expected to strategically impact on future developments in the nanoelectronics domain and their long-term applications. Crucial issues such as modelling the behaviour of these possible nanodevices and the definition of system architectures need to be addressed.

In this first issue, we therefore publish a report prepared by Prof. Mike Forshaw (University College London, UK) on the "Status of Research into Architectures for Nanoelectronic Systems in the European Research

ScienTec

Area" and the conclusions of the Working Groups (Molecular Electronics and NEMS) held during the NID15 Workshop in Madrid (February 2005).

These working groups (http://www.phantomsnet.net/Enano/ WorkingGroups.php) are open and we invite readers to contact coordinators to provide inputs & comments to improve these initiatives. The next NID16 event will take place in Glasgow (UK): June 22-24, 2005 http://www.phantomsnet.net/nidconference10.php

We also invite readers to send us their scientific contributions either as articles, reviews or publication highlights.

We would like to thanks all the authors who contributed to this issue as well as the European Commission (IST/FET/NID) for its close collaboration.

Dr. Antonio Correia PHANTOMS Foundation Editor

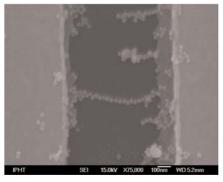

**Cover Picture:** The image shows a one micrometer gap (gold electrodes, 100 nm thick) on silicon oxide, with a single file of gold nanoparticles (30 nm diameter) captured using dielectrophoresis.

R. Kretschmer and W. Fritzsche: Pearl Chain Formation Of Nanoparticles In Microelectrode Gaps By Dielectrophoresis. Langmuir 20(2004), 11797-11801

Reprinted in part with permission from Langmuir 20, p. 11799. Copyright 2004 American Chemical Society

# EDITORIAL INFORMATION

June 2005 - Issue 1.

E-NANO Newsletter is published by PHANTOMS Foundation (Spain)

#### Editor:

Dr. Antonio Correia PHANTOMS Foundation antonio@phantomsnet.net

#### Associated editor:

Fernando Hernandez PHANTOMS Foundation fernando@phantomsnet.net

E-NANO Newsletter contains latest advances and general information about Nanotechnology including reports, scientific review articles, publication highlights, vacancies, conferences and nanonews. Letters to the editor and articles are welcome for publication.

For any question please contact the editor at: antonio@phantomsnet.net FAX: +34914973471

1000 copies of this issue have been printed.

Subscription rates (shipping included) are (Euros/year): -Europe: 100 -Non-European Countries: 150

#### Advertising:

We welcome sponsors and advertisers. Please visit http://www.phantomsnet.net/Foundatio n/advertising.php to download our media data and advertising rates.

Advertisers: Encyclopedia of Nanoscience and Nanotechnology (p. 2), ScienTec (p.7), Nanotec (p. 28), Raith (p. 28), Nanomegas (p. 30), Orsay Physics (p. 31), HWL Scientific Instruments (p. 32)

E-NANO NEWSLETTER June 2005

#### The Status of Research into Architectures for Nanoelectronic Systems in the European Research Area (RANS).

M. Forshaw and R. Stadler, University College London, Physics and Astronomy Dept., UK (m.forshaw@ucl.ac.uk)

#### Introduction

This short report is the outcome of a one-month study, funded in late 2003 by the European Commission (IST / FET), into the status of research into architectures for nanoelectronic systems. Here we use the term 'nanoelectronic system' to mean any assembly of data processing devices (electronic, magnetic, superconducting etc.) where one or more of the characteristic device dimensions is of the order of 100 nanometres or less. The reason for the study is that, although there are many nanodevices currently under investigation, there is relatively little research into how some of these devices might behave if they were to be assembled into circuits or large systems. The emphasis in this report is on large-scale digital systems. A more comprehensive EC-funded follow-on study was carried out in 2004, which also considered nanophotonic, analogue, mixed analogue-digital and other systems. The report for this later study (Nano Arch 04) is available from the first author (m.forshaw@ucl.ac.uk).

It is hoped that this report will act as a stimulus to guide subsequent activities in the field. Its original terms of reference were to provide an outline of:

- 1. Existing and proposed devices

- 2. Small and ultra-large circuits: theory and practice

- 3. Conventional architectural concepts, 'System on a chip', 3D systems et cetera.

- 4. Known problems

- 5. Unconventional and new concepts

- 6. Applications performance requirements

- 7. Availability and training of human resources

These are considered in the sections which follow, but we first discuss what we mean by "architectures for nanoelectronic systems". It has been suggested that there are five levels which must be looked at before the performance of an electronic system can properly be assessed (e.g. Meindl 01). These are:

the fundamental level (quantum effects, thermodynamic effects etc.),

the materials level (silicon, GaAs, molecular, polymer etc.),

the device level (field effect transistor, rapid single flux quantum, quantum interference, etc),

the circuit level (analogue versus digital, A-to-D converter, 64-bit full adder, memory array etc.) and

the system level (e.g. achieving Teraflops processing speed at less than 1 megawatt power dissipation).

To this one might add a sixth level, namely the application or cost level: if a device technology is not sufficiently promising for some proposed application (because it will not be faster than CMOS, or cheaper, or more reliable, or...) then it would be helpful to know this as soon as possible. Research is needed at all of these levels, although not necessarily simultaneously or with the same level of effort. Figure 1 shows that although 'nanoarchitecture' is a relatively high-level concept, it has links all the way down to individual devices and to the device technology.

In many cases research at higher levels can only be made in

very general terms, because the properties of some devices are not known sufficiently well. On the other hand some device technologies have reached a state of development where circuits with thousands or even millions of devices have been fabricated, sometimes at a near-commercial level. However, it is usually true that these large-scale circuits use devices whose technologies

Figure 1. A simplified table to show the relationship between architectures for nanoelectronic systems and other hierarchical levels, together with some of the technical requirements and the problems that have to be solved at each level

are relatively mature, and where the problems associated with the nanoscale (quantum effects, noise, fabrication problems etc.) are manageable. If these last devices were to be miniaturised, in the same way that silicon-based CMOS transistors have been miniaturised for the last thirty years, then they too would start to encounter many problems, which sometimes have no known solution.

Of course, there are many factors which have to be considered. Many of these devices - for example molecular devices - are at an early stage in their development, and there may not be enough information available to predict their performance, if they were to be combined into large structures. On the other hand, some devices - for example single-walled carbon nanotube transistors - have already been assembled into small circuits, and it is clearly necessary to start thinking about their possible performance in very large circuits. There are devices, such as polymer transistors and photonic structures, whose current dimensions are tens of micrometres, but which could well be made much smaller, or used to interface with nanoelectronic circuitry. One should also mention the major problems associated with quantum phenomena, which allow nanodevices to work, but will cause serious problems when many such devices are combined in closely-coupled circuits.

For other reviews of architectures for nanoelectronics the reader is referred to Stan 03, Waser 03 and Forshaw 04. The last paper

was partly funded as part of the present study. The updated version of the 2003 International Technology Roadmap for Semiconductors has a chapter on research devices, which contains a short section on architectures (ITRS 04).

#### 1. Existing and proposed devices

It is not the purpose of this study to review existing or proposed nanodevices in any detail, only to illustrate their spread in development status, from the device to the system level. Figure 2, which is updated from [Nikolic 03], shows that there is a spectrum of development status, from individual experimental devices to fully commercial systems that contain nanoscale features. If we suppose that the last three columns in Figure 2 ("subsystem" to "big chip") represent the domain of "nanoarchitectures", then it is clear that most devices are as yet architecturally undeveloped.

It is the opinion of some workers that many of these devices will not proceed beyond the research stage, and that those that do proceed to commercial production will be *complementary* to CMOS, rather than *replacements* for CMOS.  $10^{10}$  cm<sup>-2</sup> for logic-based circuitry and more than  $10^{11}$  cm<sup>-2</sup> for memory devices. However, it is clear that, as devices get smaller and smaller, so their maximum operating speed at high device densities, which is linked to the device power dissipation, may be often be *less* than that of present-day CMOS (see section 6 for a brief discussion and example). This implies that there may be:

*either* a limit to the number of devices on a chip (this section), *or* that parallelism will be needed (see section 3), *or* that devices with improved specifications will be needed (sec-

or that new concepts will be needed (section 5).

Not all applications require circuits with huge numbers of devices. For example, commercial applications of polymerbased transistor circuits currently require less than a few hundred devices, while many automotive or white-goods applications only need microprocessors with less than a million devices. Admittedly, these do not require nanoscale devices, but there are applications (for example, medical) where relatively small numbers of devices (less than  $10^6$ ) are needed, but in as small a volume as possible. However, the main thrust of development in Si-

| Device Name                                       | Single<br>Device | Simple<br>Circuits | Logic Gate<br>Mem. Cell | Sub-<br>system | Small<br>Chip | Big<br>Chip | Comments                               |

|---------------------------------------------------|------------------|--------------------|-------------------------|----------------|---------------|-------------|----------------------------------------|

| CMOS                                              |                  |                    | rec.                    |                |               | - I         | Approaching the scaling limit          |

| Magnetic random access memory (MRAM)              |                  |                    |                         |                |               |             | Non-volatile; no complex circuits      |

| Rapid single flux quanta (RSFQ)                   |                  |                    |                         |                |               |             | Extremely fast but needs cooling       |

| Organic transistors                               |                  |                    |                         |                |               |             | Cheap, large, slow, may shrink further |

| Resonant-tunnelling diode-HFET (III-V)            |                  |                    |                         |                |               |             | Fast, but high power                   |

| Single electron transistor (SET) memory           |                  |                    |                         |                |               |             | Small, but not yet reliable            |

| Bulk molecular logic/memory                       |                  |                    |                         |                |               |             | Potentially down-scalable              |

| Nanotube/nanowire transistors                     |                  |                    |                         |                |               |             | New devices reported regularly         |

| Quantum cellular automata/magnetic (MQCA)         |                  |                    |                         |                |               |             | Room temp.; limited results so far     |

| Resonant tunnelling diodes (RTDs) (Si-Ge)         |                  |                    |                         |                |               |             | Potentially useful but hard to make    |

| Magnetic spin-valve transistors                   |                  |                    |                         |                | _             |             | May be miniaturizable                  |

| Quantum cellular automata/electronic (EQCAs)      |                  |                    |                         |                |               |             | Low power, but very hard to make       |

| Josephson junction persistent current qubit/cubit |                  |                    |                         |                |               |             | Could be used in a quantum computer    |

| Single electron transistor (SET) logic            |                  |                    |                         |                |               |             | Circuit design/fabrication is hard     |

| Molecular (hybrid electromechanical)              |                  |                    |                         | 1              |               |             | First single-molecule transistor       |

| Quantum interference/ballistic electron devices   |                  |                    |                         |                |               |             | Problems with lack of gain             |

| Mono-molecular transistors and wires              |                  |                    |                         |                |               |             | The smallest devices possible          |

| Pre-fabrication phase no information              | 1                |                    | theory                  |                |               |             | simulation                             |

| Fabrication phase agony/struggle                  |                  |                    | working                 | demonstra      | tion          |             | commercial or available                |

tion 3).

Figure 2. Development status of various nanodevices and devices with nanoscale features. The headings 'single device...big chip' are intended to indicate in qualitative terms the relative scale of progress towards making chips with more than 108-109 devices on a chip. No attempt has been made to distinguish between devices that are suitable for logic or memory applications. Updated from [Nikolic 03].

#### 2. Small and ultra-large circuits: theory and practice

Because of the variations in their level of development, some devices have been built at the large scale, for example magnetic random access memory (MRAM) and rapid single flux quanta (RSFQ) chips; some at the small scale, for example small logic circuits with semiconductor nanowires or carbon nanotubes; and some devices have not yet been built - for example single-molecule logic circuits. The main drive for nanoelectronic circuits seems to be aimed at developing systems that have more processing power per unit volume than (future) silicon-based circuitry. This would imply device densities of the order of more than based systems lies on the axis: palmtop - laptop - desktop supercomputer, where the maximum possible number of devices is wanted, and it is probable that most nanoscale systems will be compared with, and assessed against, the nearest Si-CMOS benchmark.

Any new or proposed nanoscale circuits or systems must first be assessed against a Si-CMOS benchmark. Some applications may need only small systems, some extremely large, but no nanoscale system will be successful unless it outperforms the Si benchmark in some way (cost, speed, size, etc.).

## 3. Conventional architectural concepts, 'System on a chip', 3D systems

The term 'computer architecture' is a concept which, to some degree, is *independent* of the hardware that is used. Thus digital computers have been made using mechanical gears, electrical relays, thermionic tubes, individual transistors, integrated circuits, rapid single flux quanta devices, optoelectronic hardware, DNA-related molecules, and so on. 'Analogue' (or probabilistic-output) computers have been made using operational amplifiers, sub-threshold CMOS circuits, special-purpose digital circuitry, and simulation programs running on conventional computers; while Nature has had several billion years of development time to produce a wide range of biological data-processing structures.

In principle the term 'computer architecture' should be divorced from its practical implementations, because it is often considered to be a high-level theoretical construct. In practice the term has a significantly different meaning to different people, depending on the individual's technical background and experience. In this report we therefore take a more broad-brush approach, and allow the term to include areas such as the high-level influence of practical applications on computer design, all the way down to circuit design and individual device characteristics at the low level. Equally, we shall blur the distinction between theoretical concept and practical implementation, since it is often the case that physical and technological constraints and performance demands will affect the physical structure of a computer, while device properties may affect the layout of small-scale circuits and the classes of problems that the computer will be most efficient at solving.

| l concepts<br>g, nanoparticle arrays,<br>lecular logic, SETs,<br>CAS etc., etc.)<br>MPLEMENTARY<br>CHNOLOGIES<br>otomics, bio-CMOS,<br>as new development<br>Probable steady expansion for niche<br>applications, but possible rapid expansion<br>as new developments occur |                                                                                                             | •                      |                         |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|---|

| l concepts<br>g, nanoparticle arrays,<br>lecular logic, SETs,<br>CAS etc., etc.)<br>MPLEMENTARY<br>CHNOLOGIES<br>otomics, bio-CMOS,<br>as new development<br>Probable steady expansion for niche<br>applications, but possible rapid expansion<br>as new developments occur | MAINSTREAM CMOS IN                                                                                          | IPROVEMENTS AND        | REFINEMENT              |   |

| CHNOLOGIES applications, but possible rapid expansion — (<br>as new developments occur                                                                                                                                                                                      | xisting nanodevices<br>nd concepts<br>.g. nanoparticle arrays,<br>olecular logic, SETs,<br>.CAs etc., etc.) | Survival of the fittes | t future development    |   |

|                                                                                                                                                                                                                                                                             | MPLEMENTARY<br>CHNOLOGIES<br>otonics, bio-CMOS,<br>stic electronics etc.)                                   | applications, but p    | ossible rapid expansion | Ļ |

Figure 3. Possible timelines for future nanoelectronics development. Architectural factors as described in the text will apply to all of the timelines. The relative width of the bars has no special significance. (from Nano\_Arch 04)

Such interactions at all levels between device characteristics, application requirements and technological constraints, and architecture (Figure 3), will be as important for post-CMOS systems as they are for present-day CMOS systems.

People have been investigating and developing computer architectures for sixty years, trying to increase their performance. There have been tens of thousands of publications in this area, and it is not the purpose of this report to review the field in detail. As far as architectures for nanoelectronic systems are concerned, the most relevant concepts are:

**Parallelism** - the use of more than one processing element, often identical and arranged in a relatively simple geometry such as a rectangular mesh or perhaps a more complicated geometry such as a hypercube or a fat tree. Parallelism *sometimes* offers massive speed increases over a single, general-purpose processor. Modern PCs or workstations, although they use limited forms of parallelism, are lineal descendants of the original, von Neumann, single-processor concept. Parallelism also offers the possibility of using huge numbers of relatively small, slow, processing elements to outperform fast, powerful, single processors. However, the single-processor concept has the advantage of flexibility – it can in principle be programmed to solve any problem – whereas highly parallel systems are sometimes very inefficient, except when they are designed to solve specific classes of problem.

**Specificity** - tailoring of the hardware to match the requirements of a particular algorithm - for example, the Fast Fourier Transform, or image processing tasks - and thereby to achieve the maximum possible speed. The disadvantage of this speedup is that the hardware is no longer 'general purpose' – the only calculation that it can carry out efficiently is the chosen algorithm. This limitation can partly be avoided by using reconfiguration techniques.

**Reconfiguration** - the ability to 'rewire' a generic arrangement of simple elements (memory or logic) to implement some desired function. Existing memory chips have a simple form of reconfiguration - spare rows or columns of memory cells can be switched to replace cells that are found to be defective during manufacturing. A more sophisticated form of reconfigurability is available through the use of (Field) Programmable Gate Logic Arrays (FPGLA). In the context of nanoelectronic systems, perhaps the most famous example of a reconfigurable computer system was the Teramac, which also demonstrated an implementation of fault tolerance.

**Fault tolerance** - the ability of a computer system to operate reliably, even if many of its individual components suffer from manufacturing defects, from in-service failures, or from random transient errors. Fault tolerance requires the use of an architecture which can implement whichever fault tolerance algorithm has been chosen. The term 'fault tolerance' is sometimes invoked as a mantra, in the belief that useful, high-performance, nanoelectronic systems can eventually be developed, no matter how defective or faulty the individual nanoscale components might be. This belief should be treated with considerable scepticism: in some cases, fault tolerance may require such large numbers of spare components that the resulting system may be *less* efficient than a system that uses larger but more reliable components.

**System on a chip** - the integration of different technologies on a single chip. These could be different digital technologies (CMOS, Si-Ge, III-V), or mixed analogue (photosensors, chemical or biosensors) and digital; optoelectronic; mechanical (NEMS/MEMS); hybrid systems (CMOS/molecular); etc.

**Asynchronous operation** - it has long been known that digital systems do not need to have a master clock, but it is only recently, with increasing power and space demands involved in generating chip-wide clock signals, that systems which use local clocks and data handshaking, have started to look attractive.

**Short range data/control signals** - this concept overlaps that of asynchronous operation. Instead of having a master controller to distribute control signals over the whole of a chip, it is possible in

some circumstances to have only a limited number of master control lines, and to rearrange the system layout so that individual processing elements in a large array operate semi-independently from one another. This concept is related to the MIMD – SIMD classification of computer types. MIMD stands for Multiple Instruction, Multiple Data: a network of PCs in an office is an example of an MIMD system. SIMD stands for Single Instruction, Multiple Data – the 'retina-like' CLIP (cellular logic image processing) arrays of the 70's and 80's, and the more recent CNN (cellular neural network) systems, are examples of SIMD systems. 'Neuromorphic' systems can be considered to be extensions of CLIP or CNN concepts, which in turn overlap with fault tolerant cellular automata structures (e.g. [Peper 03]).

Finally we may mention 3D systems. The main advantage of '3D' systems is that one can pack more devices into a given footprint: the main disadvantages are that it is relatively hard to send signals throughout the volume, and heat dissipation problems rapidly increase in severity. The simplest way to make a 3D system is to stack 'ordinary' chips on top of each other: this has been done with conventional Si-based chips for many years, and in a variety of ways. Two chips can be relatively easily connected 'face-to-face' using 'flip-chip' techniques, but until recently stacks of three or more chips have mainly been connected 'edge-to-edge'. A recent EC-funded project examined ways to provide through-chip vias and 'face-to-face' molecular wiring between chips [Crawley 03]: a book on this subject was published in October 2004 [Crawley 04]. There has been a recent US DARPA call for proposals to develop 3D stacks of (Si-CMOSbased) chips.

There is a large body of existing literature on architectural concepts, but new techniques continue to appear. The application of both old and new ideas to nanoelectronic systems has only just started.

#### 4. Known problems

More and more problems have to be overcome as device sizes approach the nanoscale. The most dramatic evidence for this, at least for Si-CMOS devices, is presented in the ITRS Roadmap tables, where unsolved problems are shown as 'red brick walls' [ITRS 04]. The same will be true for any other nanodevice, nanocircuit, nanoarchitecture or nanosystem. In general terms, the problems are quite well understood: they range from quantum effects to reliability problems, as shown schematically in Figure 1 in the Introduction. It is (sometimes) relatively easy to analyse one problem in isolation. For example, a single-electron transistor at zero Kelvin, with 'perfect' contacts and power supply, can be analysed to a fair degree of accuracy; or the quantum mechanical probability of electron transmission near equilibrium through a small molecule at zero Kelvin, again with 'perfect' contacts. However, it is much harder to include finite temperature effects, non-equilibrium electron transport and the existence of many similar devices in close physical contact. Yet again, at the other end of the scale, fault tolerance techniques have been developed over many years, but the effects of defects or transient errors on the performance of large nanosystems have yet to be examined.

It is not the aim of this report to provide an exhaustive analysis of these problems. Here we present instead two simple examples to show that there are many problem areas where much further work is needed before the properties of nanocircuits and nanosystems can be predicted with any degree of certainty.

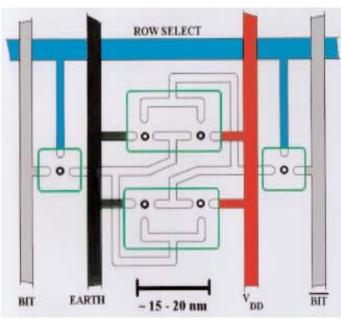

The first example is illustrated in Figure 4, which shows a hypothetical six-transistor memory cell with six singleelectron transistors (SETs). The small circles represent the islands of the SETs. In a 6T memory cell using conventional Si transistors, a first-order analysis of the circuit behaviour is (relatively) straightforward, because the inputs and outputs are more or less isolated from each other. However, Figure 4 shows that the SET layout will behave as a distributed capacitative network, whose analysis is complicated even further by the quantum blockage effects involved in the SET operation. This picture (of an unworkable circuit!) is intended only to illustrate how electrical coupling between neighbouring conduc-

Figure 4. A hypothetical single-electron transistor 6T memory cell.

tors and distributed capacitances may start to dominate circuit operation as devices and wiring become smaller and smaller. In general the electrical isolation between the input and output of any device becomes worse as the device shrinks in size. Circuit design techniques to analyse distributed capacitative or electromagnetic coupling effects at a classical level are relatively well developed, and the theory of SET operation in, for example electron pump circuits, is quite well understood, but nobody has yet tried to analyse the combination of multiple–SET circuit behaviour with distributed capacitative effects.

Our second example is taken from the field of fault tolerance and error correction. The problem of error correction for nanodevices and nanocircuits is not an academic one, whose possible consequences can be ignored for ever. Even presentday CMOS chips, with minimum feature sizes in the 130 -90 nm range, now have to take account of soft errors due to radioactive decay products and cosmic rays. Much 64-bit on-chip memory now has error coding and correction (ECC) built in to overcome soft errors, and as devices get smaller so soft error rates (SER) will go

up. To quote from a recent paper (Baumann02). "SER has become a huge concern in advanced CMOS products because, uncorrected, it induces a failure rate higher than all the other reliability mechanism combined".

So far CMOS logic devices, which typically use larger-than-minimum features than memory, have not been of such concern, but SER in CMOS logic is also becoming a problem. The use of triple

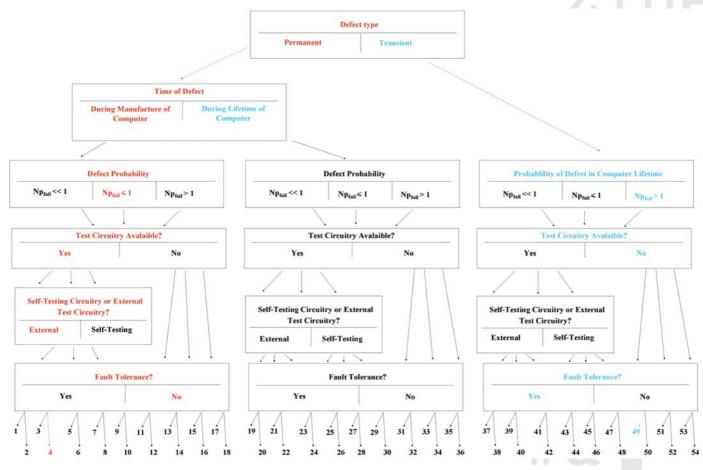

Figure 5. A simplified flow chart to illustrate the variety of strategies that can be adopted, given the possibility of permanent defects or transient errors in a (nano) electronic system. The left path is representative of the present-day strategy for producing reliable memory chips (using spare rows or columns of memory cells). An example of the strategy involved in the right path is the use of Triple Modular Redundancy (TMR), which is used in passenger aircraft flight control computers.

modular redundancy (TMR), with three copies of the logic circuitry, is being talked about, even for one-chip single-user commercial operation [Baumann 02].

If fault tolerance and error correction are needed for present-day CMOS chips, where transistors have minimum feature sizes of 130 -90 nm, then it is clear that future nanoelectronic systems will have an even greater need for careful design to protect against hard and soft errors. Once again, relatively little work has been carried out in this area. Figure 5 shows that a wide range of strategies are available, with some being more effective than others (N denotes the number of

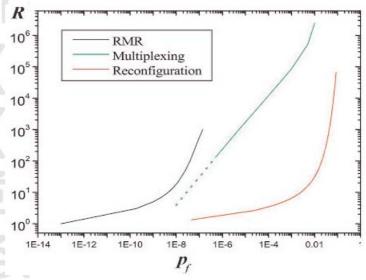

Figure 6. Comparison of three fault tolerance strategies in protecting a hypothetical chip with 1012 nanodevices against permanent manufacturing defects. R is the redundancy factor (the number of copies of each device or circuit), and pf is the failure rate per device. From [Nikolic 02]. See text for details. Recent work (2004, 2005) has shown that reconfiguration can provide dramatically improved results, i.e. moving the red curve rightwards and downwards

devices involved,  $p_f$  denotes the failure rate per device). It will certainly be necessary to combine more than one strategy if reliable nanosystems are to be produced. There are relatively few different techniques available for providing fault tolerance. Figure 6 illustrates the underlying problem. Suppose that one wanted to manufacture a chip with 10<sup>12</sup> nanodevices, each having a manufacturing failure rate  $p_f$ . Three techniques are compared – Rfold Modular Redundancy (an extension of TMR), von Neumann's multiplexing technique, and system reconfiguration (cf. [Nikolic 01, 02]). Figure 6 shows that the best protection against manufacturing faults is reconfiguration. However, to produce chips with a 90% probability of working (for example), if the manufacturing defect rate for an individual device is 10%, a factor of at least 30-fold device redundancy is needed, and this factor does not include the extra redundancy needed to make the system reconfigurable in the first place. To achieve three-fold redundancy (again, for example), a device failure rate of less than ~10<sup>-5</sup> will be needed. This is only slightly less challenging than the failure rate of present-day CMOS devices (which is, *very* approximately, in the range  $10^{-6}$  to  $10^{-7}$  per device). We note in passing that much has been talked about about the possibilities of self-assembly for making nanoscale circuits and systems, particularly for molecular devices. However, there have as yet been very few demonstrations of the controllability or reliability of self-assembly.

Analysis tools for individual nanodevices exist, but with varying degrees of analytical approximation. Tools for nanoscale circuits containing tens or hundreds of devices are as yet very primitive or nonexistent. At the system level, the effects of manufacturing defects or transient in-service errors will make very severe demands on the amount of circuit redundancy that will be needed for reliable operation: these constraints have yet to be analysed fully.

#### 5. Unconventional and new concepts

10

In the field of nanoelectronic systems there is almost no such thing as a completely new concept: almost all "new" ideas have their origins in earlier concepts (Feynman's "There is always room at the bottom" perhaps being the exception). In this section logue data processing with digital processing has also been shown (in principle) to offer advantages in terms of efficiency in speed and in heat dissipation [Sarpeshkar 98]. Many more 'exotic' concepts have been described – for chemical computers, DNA computers, microfluidic processors and so on. These will be considered in the briefly in the following sections.

Extensive research on animal brains has demonstrated their superlative efficiency in power consumption, in parallelism and in processing power [Laughlin 03], but so far there have been few attempts to make close copies of the complex bio-electrochemical processes involved. Some of the principles involved in neuronal processing have, however, been copied extensively, in all sorts of ways, from software neural networks running on conventional computers, to the use of subthreshold CMOS devices working like synthetic neurons, and on a variety of mesh-connected computers that emulate some aspects of the visual retina and/or higher-level cortical processes (e.g. CLIP, CNNs).

It was shown more than thirty years ago that the cellular automaton game 'Life' was a universal computer, and students at MIT modelled a logic gate using Life. However, it occupied about a million cells. Very regular arrays of very simple processing elements are usually very inefficient at solving real-world problems, although systems using two-dimensional arrays of nanoparticles continue to be described and analysed (e.g. [Csaba 01], [Basu 04]). The choice is to move away from perfectly regular meshes, while still using cells with very simple properties - the quantum cellular automata (QCA) approach - or to use regular meshes of cells with more processing power in each unit - the CNN approach. So far the QCA approach appears to be subject to a variety of serious problems, not only in implementation, but also in performance [Parish 03]. Similarly, as anyone who has designed, built or used a highly-parallel processing engine will know, cellular nonlinear (or neural) networks (CNNs) are intolerant to device failure, which is likely to be extremely important with future nanodevices. It is equally difficult to avoid problems with system clocking and data distribution, although several asynchronous array structures have been proposed as possible candidates for nanocomputers (e.g. [Peper 03, Peper 04]). Thus the trend in cellular logic, CNN, and cellular automata research has been towards building-in fault tolerance.

we briefly discuss some unconventional ideas and 'new' concepts, but it should be appreciated that these sometimes have a previous history of development.

Although analogue computers largely gave way to digital computers, they have never completely disappeared, and they may offer some significant advantages at the nanoscale. Certainly, analogue-digital circuitry has undergone a significant expansion over the last few years. Some cellular neural network (CNN) chips have mixed analogue and digital circuitry, and the System-ona-Chip concept is largely aimed at combining analogue sensors with digital processing. Combining ana-

#### E-NANO NEWSLETTER June 2005

#### Some new ideas

Many interesting ideas have been put forward over the last few years. Some of them have been aimed at protecting nanoelectronic systems against manufacturing faults or against transient faults that might occur in-service. We present here some extremely brief descriptions of these different ideas.

It is generally accepted that nanoelectronic systems will probably have to have extremely regular structures (like cellular automata or CNNs), so that they can be made easily, perhaps using self-assembly techniques (see below). Because of the inherent attractiveness of the ideas behind field-programmable gate arrays (FPGAs), some concepts have combined the regularity of CNNs and FPGAs at the local scale with the assumption that larger-scale structures will look like reconfigurable systems.

Likharev has proposed a relatively complex architecture, which is based on regularly structured elements which are laid out in a crossbar geometry [Likharev 04]. The details are too complex to go into here, but the processing elements are essentially 'neurons' with a relatively standard sum-and-threshold behaviour. It is assumed that the processing devices will be single-electron transistors and single-electron traps which act as local memory. High performance levels in the presence of defective or noisy devices have been reported.

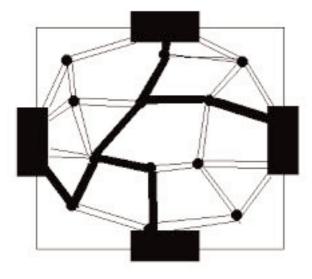

The NanoCell concept is illustrated in Figure 7. A 'large' region of insulated substrate is filled to a suitable density with a sparse layer of nanoparticles, then molecular wires are quasi-randomly deposited on top, so that some of them touch the nanoparticles and some of them touch a number of contact pads at the edge of the region. By application of appropriate programming voltages at the I/O pads, conducting paths can be established in such a way as to implement various logic functions.

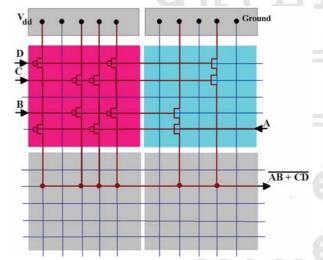

Another new idea is illustrated in Figure 8 [Snider 04]. Complementary p-type and n-type transistors are formed at the

Figure 7. The Nanocell concept. Nanoparticles (black dots) are randomly deposited within the rectangular region, which has four input-output pads (black rectangles). Molecular wires are then deposited over the nanoparticles. Some of these will bridge pairs of nanoparticles, or nanoparticles and the I/O pads. Programming voltages are applied to selected pairs of pads to turn some of the molecule-particle contacts into negative-differential (NDR) switches. See [Husband 03] for details.

crosspoints of a regular grid of metallic, p-type and n-type wires. Simulations indicate that defect-tolerant, PGLA-like circuits could be formed, even with defect rates as high as 10%. A different approach to fault tolerance, which still uses a large degree of structural regularity, is the NanoBox Processor Grid concept, which is based on regularly patterned, regularly organised, nested 'black boxes' containing error-correcting lookup tables. High levels of reliability, in the presence of large numbers of errors, are reported [KleinOsowski 04].

Yet again, another crossbar structure has been described in [Ziegler 03], where it is assumed that there will be diodes at the

Figure 8. CMOS-like logic based on metallic wires (all horizontal wires), p-type wires (leftmost five vertical wires) and n-type wires (rightmost five wires), with p-type and n-type FETs formed at selected junctions. A chemical layer between the wire planes determines the type of device that can be formed at each junction. A typical separation between junctions might be 30 nm. Simulations suggest that the structure should provide defect-tolerant, reconfigurable PGLA-like circuits, even for device defect rates of ~10%. It is suggested that the circuit density could be 100 times higher than existing FPGAs (after [Snider 04]).

crossbar junctions, with CMOS circuitry provided at the periphery of the structure to provide gain, circuit control, and I/O functions.

Another method for producing reliability in digital logic circuits is to use replicated 'neurons' in small feed-forward neural networks, whereby the thresholding operation of the network produces the desired Boolean output: the devices are not specified in detail [Schmid 03].

Although these ideas are interesting and potentially useful, it must be emphasised that almost in every case it is assumed that some device – typically a transistor – can be formed, with moderate reliability, where it is needed. These assumptions remain to be proved.

In almost every proposed nanosystem the concept of selfassembly appears, either explicitly or implicitly. It is assumed that methods exist (and sometimes this is true) for aligning nanoparticles or nanowires where they are required. An additional lower stratum of self-assembly is also needed – the nanoparticles or nanowires have themselves to be formed by self-assembly, preferably with extreme accuracy if undesirable variations in device properties are to be avoided. Much research and development is needed before these ideas can be fully verified.

What we have described above, albeit briefly, probably represents the main thrust of architectural (and circuit) development: regular, simple structures, where some degree of defective devices can be tolerated. Sometimes the thrust is towards neuromorphic architectures, sometimes it is directed towards PGLAlike structures.

There are in addition a number of other concepts which have been proposed, based on other technologies. Some of the most interesting of these are based on the use of DNA molecules. For example, by growing DNA tiles on a flat substrate, with the intermolecular contacts being directed by 'sticky' ends, Boolean operations such as cumulative XOR have been demonstrated, although the timescale (hours) and the reliability (~98.4%) suggest that scaling this mechanism up to much larger and faster systems will be difficult [Mao 00]. An interesting demonstration of DNA computing [Benenson 01] was the implementation in solution of a finite state automaton, with two ATP molecules being consumed at each step, with an energy loss of  ${\sim}10^{-19}$  J, at a 'clock rate' of  $\sim 10^9$  Hz. There is, however, a long way to go before such systems would be economically viable. Other papers on this subject can be found in, for example, [Owenson 01].

Finally, and for completeness, we mention that in principle computing structures could be built using nanomechanical or microfluidic components, if they could be made small enough. A microfluidic processing structure with ~500 gates has been built and tested [Groismann 03].

#### 6. Performance requirements

Most of the fundamental limits to the performance of conventional computing systems have been known for many years (e.g. Waser 03), but much work has yet to be carried out before these limits can be reached, and there are several factors whose effects are perhaps not widely known. Here we present just one simple example to illustrate how high-level and low-level factors combine to place restraints on the properties of nanodevices and nanoarchitectures if the ultimate computational limits are to be achieved.

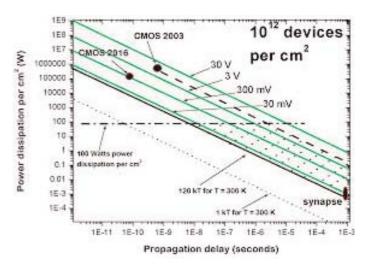

Figure 9 is based on the assumptions of a hypothetical 1 cm<sup>2</sup> chip, working at 300K and containing 10<sup>12</sup> nanodevices, The axes of the diagram are the mean power dissipation per cm<sup>2</sup> and the pulse duration: it is assumed that the mean switching probability is 10% for every device The symbol marked 'CMOS 2003' shows that, even if it were possible to pack 10<sup>12</sup> present-day CMOS devices into an area of 1 cm<sup>2</sup> (which it is not!), then the power dissipation would be ~1 MW . Using the ITRS Roadmap estimates of future Si-based devices - the 'CMOS 2016' symbol - would only reduce the power dissipation by about a factor of 10. The horizontal line marked '100 Watts power dissipation per cm<sup>2</sup> ' represents a realistic estimate of the maximum allowable power dissipation per unit area (no matter what the device technology). The lower, dotted diagonal line marked '1kT for T = 300K' represents the thermal fluctuation limit - any system operating along this line will have every one of its devices failing approximately 50% of the time. The line marked '120kT' is a more practical limit: it corresponds to systems which have, on average, one device failing once per year. Only those systems whose power dissipation and pulse duration lie within the hatched region will have a better performance than systems based on present-day CMOS devices. In addition, only those systems which operate near the '120kT' black diagonal line will achieve the maximum theoretical performance. Such systems will have to use large amounts of parallelism.

The green diagonal lines, marked '30V, 3V....30mV' are the result of further constraints imposed by shot noise fluctuations, which are additional to thermal noise constraints. Briefly, shot

noise can only be kept under control if each signal pulse contains at least 500 electrons. It can be shown (Forshaw 03) that if the practical thermal limit of ~120kT is to be approached, then shot noise control demands that the system operating voltage (V<sub>DD</sub> in CMOS terminology) must be of the order of 30 mV or less.

Figure 9. Plots of the maximum voltages (green diagonal lines), above which a system with 1012 devices per cm2 will fail catastrophically often, as a function of the pulse duration (or propagation delay per device) and the power dissipation per cm2. Devices in the hatched area will potentially have better performance than current CMOS devices, provided that system parallelism can be used to overcome their low operating frequency.

Much work remains to be done, to assess how best to achieve the maximum possible performance for a system with particular nanodevices, arranged in an appropriate nanoarchitecture, in order to implement a specific algorithm or set of algorithms.

#### 7. Availability and training of human resources

Time constraints have prevented more than a token investigation into this topic, which was explored in detail in the follow-up study [NanoArch04]. However, it is clear that, while many European universities and research institutes (and indeed American and Pacific Rim establishments) are investing effort into nanotechnology in general, there are relatively fewer establishments that are investigating nanoelectronic systems in general, and even fewer who are explicitly including nanoarchitectural considerations in their research remit.

There are three obvious reasons for this. One is that the term 'nanotechnology' covers an enormous field, and 'nanoelectronics', although more restricted in its meaning, still covers a very wide range of research options. It is not financially possible, on a national or even supranational scale, to fund all of the possible research avenues. The second reason is that nanoarchitectural research has only recently been understood to have important practical implications for the development of nanoelectronic devices and systems. Thirdly, nanoarchitecture research, to be carried out successfully, requires a very wide range of multi-disciplinary skills, preferably in one individual, at the least in small active research groups. Such ideals are, alas, rarely achieved, but they must be aimed for, by appropriate training and development. There are signs that new device ideas are needed, because high-level architectural and system considerations suggest that many existing devices will fail to develop into useful systems. Responses to a questionnaire in an EC study [NanoArch04], and discussions with the correspondents, suggest that there is sufficient experience at an intermediate/high level to provide ade-

quate training in this area, although there is a shortage of welltrained European students. Summer schools, and possibly a focused network, would probably help provide the necessary increase in broad-based knowledge for research and development in this area.

Nanoelectronic architecture research, to be carried out successfully, requires a very wide range of multi-disciplinary skills, preferably in small active research groups.

#### 8. CONCLUSIONS AND RECOMMENDATIONS

More or less every country in the EU is investing in nanotechnology research and development; many are investing in nanoelectronics; and one or two are thinking about investing in nanoarchitectures. It is the opinion of some workers that many currentlyproposed or experimental nanodevices will not proceed beyond the research stage, and that those that do proceed to commercial production will be *complementary* to CMOS, rather than *replacements* for CMOS.

Any new or proposed nanoscale circuits or systems must first be assessed against a silicon CMOS benchmark. Some applications may need only small systems, some extremely large, but no nanoscale system will be successful unless it outperforms the Si benchmark in some way (cost, speed, size, etc.).

There is a large body of existing literature on architectural concepts, but new techniques continue to appear. The application of both old and new ideas to nanoelectronic systems has only just started.

Analysis tools for individual nanodevices exist, but with varying degrees of analytical approximation. Modelling tools for nanoscale circuits containing tens or hundreds of devices are as yet very primitive or nonexistent. At the system level, the effects of manufacturing defects or transient in-service errors will make very severe demands on the amount of circuit redundancy that will be needed for reliable operation: these constraints have yet to be analysed fully.

Much work remains to be done, to assess how best to approach the theoretical limits of performance for a system with particular nanodevices, arranged in an appropriate nanoarchitecture, in order to carry out a specific algorithm or set of algorithms. Nanoelectronic architecture research, to be carried out successfully, requires a very wide range of multi-disciplinary skills, preferably in one individual, at the least in small active research groups.

We suggest that the following actions would help in the future development of architectures for nanoelectronic systems:

A rigorous investigation should be made, where possible, into which existing or proposed nanodevices will provide better performance in the future than CMOS-related devices, when assembled onto high-density chips (i.e. with more than ~10<sup>10</sup> devices). The analysis should be divided into three categories, namely logic, memory, and CMOS-complementary systems (e.g. sensors, optical interfaces, SoC).

For devices where sufficient information may not be available (e.g. molecular-scale or CNT devices), the funding of research should continue, to allow their performance to be assessed.

More attempts should be made to fabricate small 'circuit-level' systems, where several devices and input-output structures are combined at a true nano-scale.

The fabrication of such small systems should be done in combination with analysis/simulation of the behaviour of these structures. This quasi-mesoscopic region, where quantum mechanical coherence and decoherence phenomena overlap with classical effects (capacitative coupling, thermal fluctuations) is extremely difficult to analyse properly, but the development of molecular-scale devices and systems will depend on the availability of adequate modelling tools.

It is becoming increasingly likely that there will be a divergence between systems that are based on more-or-less conventional digital logic, where 100% reliability is desired, and systems (notably for pattern recognition of various kinds) where analogue/probabilistic principles are involved and less than 100% reliability is acceptable. At present such 'soft' systems are almost exclusively implemented as software running on conventional computers. It is possible that some nanoscale devices/systems will be intrinsically analogue/probabilistic in nature, and/or be prone to errors which would make them unsuitable for digital logic applications. More efforts should therefore be made to see if such 'soft' systems will offer any better performance than CMOS-based systems. These soft systems might be nanoelectronic in nature, or nanophotonic, or perhaps some combination of these with sensors.

'Blue sky' research into new nanodevices/systems should be encouraged, to improve the chances of reaching the ultimate performance limits of conventional and/or analogue computing.

#### ACKNOWLEDGEMENTS

This report was funded by the European Commission (ISF/FET - NID Proactive - IST-2000-26021 Phantoms Network Contract). Authors wish to thank the 'PHANTOMS Foundation' in editing this report for publication.

Figure 3 and some of the material in the Conclusions section are from the follow-on study (Nano\_Arch\_Review, EC FP6/2002/IST/1 Contract No 507519)

#### References

[Basu 04] A. Basu et al., 'A comprehensive analytical capacitance model of a two dimensional nanodot array', IEEE Computer Society, Proc. 5th Int. Symp. on Quality Electronic Design, 2004, 259-264, 2004.

[Baumann 02] R. Baumann, 'The impact of technology scaling on soft error rate performance and limits to the efficacy of error correction', pp 329-332, IEEE Intl. Electron Devices Meeting 2002 IEDM '02 Digest, 8-11 Dec. 2002.

[Benenson 01] Y. Benenson et al., 'Programmable and autonomous computing machine made of biomolecules' *Nature* 414, 430-434, 2001.

[Csaba 01] G. Csaba, A. I. Csurgay, and W. Porod, "Computing architecture composed of next-neighbor-coupled optically pumped nanodevices," *International Journal of Circuit Theory and Applications* **29**, 73–91, 2001.

[Crawley 03] D. Crawley et al., 3D molecular interconnection technology, *J. Micromech. And Microeng.* 13 (5), 655-662, 2003.

[Crawley 04] D. Crawley, K. Nikolic and M. Forshaw (eds), *3D Nanoelectronic Computer Architecture and Implementation*, IoP Press, London, UK, October 2004.

[Forshaw 04] M. Forshaw, R.Stadler, D. Crawley and K. Nikolic, A short review of nanoelectronic architectures, *Nanotechnology* 15, pp. S220-S223, 2004

#### www.phantomsnet.net

E-NANO NEWSLETTER June 2005

[Groisman 03] A. Groisman, M. Enzelburger and S.R. Quake, Microfluidic memory and control devices, *Science* 300, 955-958, 2003

[Husband 03] C.P. Husband, S.M. Husband, J.S. Daniels and J.M. Tour, 'Logic and memory with Nanocell circuits', *IEEE Trans. Electron Dev.* 50, 1865-1875, 2003.

[ITRS 04] International Technology Roadmap for Semiconductors, 2004 update, Emerging Research Devices chapter, <u>http://public.itrs.net</u>

[KleinOsowski 04] A.J. KleinOsowski et al., 'The recursive NanoBox processor grid: a reliable system architecture for unreliable nanotechnology devices (ajko@mail.ece.umn.edu)

[Laughlin 03] S. Laughlin and T.J. Sejnowski, Communication in Neuronal Networks, Science 301, 1870-1874, 2003

[Likhaarev 04] O. Turel, J.H. Lee, Ziaoolong Ma and K.K. Likharev, 'Nanoelectronic neuromorphic netwroks (CrossNets): new results', (Likharev home page at cc.sunysb.edu)

[Mao 00] C. Mao, T.H. LaBean, J.H. Reif and N.C. Seeman, 'Logical computation using algorithmic self-assembly of DNA triple-crossover molecules', *Nature* 407, 493-496, 2000.

[Meindl 01]J.D. Meindl, Q. Chen and J.A. Davis, Limits on Silicon Nanoelectronics for Terascale Integration, *Science* 293, 2044-2049, 2001

[Nano\_Arch04] M. Forshaw, D. Crawley, P. Jonker, J. Han and C. Sotomayor Torres, A Review of the Status of Research and Training into Architectures for Nanoelectronic and Nanophotonic Systems in the European Research Area, FP6/2002/IST/1 SSA, Contract no. 507519, July 2004 (available from m.forshaw@ucl.ac.uk).

[Nikolic 01] K.Nikolic, A. Sadek and M. Forshaw, Architectures for reliable computing with unreliable nanodevices, Proc.1st IEEE Conference on Nanotechnology. IEEE-NANO 2001, 254-259, 2001

[Nikolic 02] K.Nikolic, A. Sadek and M. Forshaw, Fault-tolerant techniques for nanocomputers, *Nanotechnology* 13 (3), 357-362, 2002

[Nikolic 03] K.Nikolic, M. Forshaw and R. Compañó, 'The current status of nanoelectronic devices', *Int. J. Nanosci.* 2, 7-29, 2003.

[Owenson 01] G.G. Owenson et al., 'DNA-based logic', *Soft Computing* 5, 102-105, 2001.

#### ANNOUNCEMENT

[Parish 03] M.C.B. Parish and M. Forshaw, 'Physical constraints on magnetic quantum cellular automata', *Appl. Phys. Lett.* 83, 2046-2048, 2003

[Peper 03] J. Lee, S. Adachi and S. Mashiko, Laying out circuits on asynchronous cellular arrays: a step towards feasible nanocomputers?, *Nanotechnology* 469-485, 2003.

[Peper 04] F. Peper et al., Fault-tolerance in nanocomputers: a cellular array approach, *IEEE Trans. Nanotech.* 3, 187-201 2004

[Sarpeshkar 98] R. Sarpeshkar, Analog versus Digital: Extrapolating from Electronics to Neurobiology, *Neural Computing* 10, 1603 – 1638, 1998.

[Schmid 03] A. Schmid and Y. Leblebici, 'A modular approach for reliable nanoelectronic and very-deep submicron circuit design based on analog neural network principles', Proc. IEEE-NANO 2003, pt 2, 647-650, 2003 (Cat. No.03TH8700)

[Snider 04] G. Snider, P. Kueckes & R.S. Williams, 'CMOS-like logic in defective, nanoscale crossbars', *Nanotechnology* 15, 881-891, 2004.

[Stan 03] M. Stan, P.D. Franzon, S.C. Goldstein, J. C. Lach and M. Ziegler, Molecular Electronics: From Devices and Interconnect to Circuits and Architecture, Proc. IEEE 91, 1940-1957, 2003

[Waser 03] R. Waser (ed), Nanoelectronics and Information Technology, Wiley-VCH 2003, ISBN 3-527-40363-9.

[Ziegler 03] M.M. Ziegler and M.R. Stan, 'CMOS/Nano Co-Design for Crossbar-based Molecular Electronic Systems', IEEE Trans. Nano. 2, 217-230, 2003.

Footnote: It must be emphasised that the contents of this report represent the personal views of the authors. Because of the report's brevity, many topics receive no more than a mention: this should in no way be taken to be an indication of the relative importance of such topics. Due to time constraints, only a small number of references are provided: please contact the authors if individual references are needed.

## NID 16 Workshop. 22 - 24 June, 2005 (Glasgow, UK)

The NID 16 Workshop will be organised by the University of Glasgow in collaboration with the European Commission (IST/FET/Nano) and the PHANTOMS Foundation.

The Workshop will be held in Glasgow, one of the most magnificent "Victorian" cities in the world and only a short journey from Scotland's scenic west coast.

The NID 16 workshop will gather participants from several projects funded by the NID pro-active initiative (part of the European Union's IST research programme). There will be a Plenary session during which presentations from the EU projects under review and invited talks from experts outside the NID initiative will be given. There will also be working group sessions focused on the application of a broad range of nano-scale technologies such as information processing and on the prospects for replacing mainstream approaches, such as CMOS.

See more information about this event at http://www.phantomsnet.net/nidconference10/

#### 15th NID: PRESS RELEASE

#### Life beyond CMOS

"For the last 40 years computers have been getting faster as CMOS chips have become smaller, faster and cheaper. But all good things come to an end and, all around the world, people have begun looking at alternative electronic devices that might follow on from CMOS."

So said Dr Michael Forshaw, coordinator of IST project **ESCH-ER**, who gathered with other researchers to present recent findings in the search for new technology to succeed CMOS (complementary metal oxide semiconductors), during the 15th Nanotechnology Information Devices (NID) Workshop, organised by the **PHANTOMS Foundation** based in Madrid.

CMOS has been the dominant chip technology used by the world's electronics industry for several decades. CMOS semiconductors use both negative and positive polarity circuits. Since only one of the circuit types is on at any given time, CMOS chips require much less power than chips using just one type of transistor. This makes them particularly attractive for use in batterypowered devices, such as portable computers.

#### **Getting smaller**

Since their introduction, CMOS transistors have shrunk exponentially in size in accordance with Moore's Law. This law predicts a doubling of transistors per integrated circuit every 18 months. However, the ability to scale down CMOS further appears to be reaching physical and technical limits. The International Technology Roadmap for Semiconductors (ITRS), a worldwide organisation responsible for identifying the technological challenges and needs facing the semiconductor industry, predicts the size limit for CMOS technology to be 5 to 10 nm. Furthermore, ITRS believes this limit will be reached in 15-20 years time.

Semiconductor industries such as Intel in the US and Infineon, STMicroelectronics and Philips in Europe are now developing the factories for CMOS chips with 65 nm size features, the `65 nm node', which ITRS foresees in full production in 2007. To meet future needs of the electronics industry, ITRS has set semiconductor manufacturers the target of producing 45 nm CMOS technology nodes, or junctions, by 2010. However, to manufacture CMOS technology below 65 nm, new fabrication treatments are needed. "The problem with conventional thermal treatments," explained Dr Vittorio Privitera of Consiglio Nazionale delle Ricerche (CNR), "is it is not possible any more to achieve the junction depths and the special characteristics of the dopant layer that are required."

Privitera is the coordinator of the **FLASH** project, which has been developing a new laser-based treatment, called excimer laser annealing (ELA), to meet the ITRS target. Initial results have been extremely encouraging. "The laser is able to make ultrashallow junctions with dopant profiles which are extremely sharp and electrically very active. This is the first time that this has been done," reported Privitera. Over the course of 2005, Privitera and his partners intend to construct and evaluate a prototype production line for fabricating MOSFET transistors using the new method.

Recently completed project **NEAR** was also at the workshop. NEAR aimed at developing new non-CMOS nanoelectronic devices that are extremely compact, consume low power and operate at room temperature. Two component types were inves-

#### www.phantomsnet.net

tigated, known as Three Terminal Ballistic Junction (TBJ) devices and Self Switching Devices (SSD). During the project, basic logic circuits were created using TBJ and SSD devices, and successfully operated at room temperature.

#### Looking to the future

Discussing future directions in mono-molecular electronics, the name given to digital logic circuits designed using single molecules, Dr Christian Joachim, a Research Director at the Centre National de la Recherche Scientifique (CNRS) and **CHIC** project partner, described the majority view that: "We have decided to take a bottom-up approach, starting with atoms and asking ourselves 'what do we need?' or 'what is the minimum sized molecule to implant a computation inside it?'" Amongst the key issues to be tackled are: what computing resources are available, how information can be exchanged internally, and what cooling and energy requirements there are.

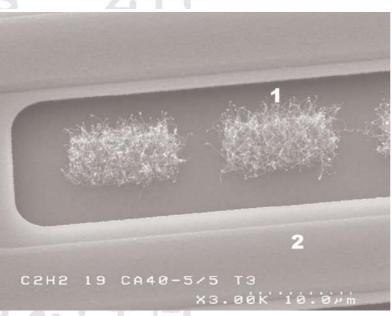

Another area covered at the event was alternative electronics, investigating devices that could replace CMOS beyond the 10 to 5 nm frontier and provide at least comparable performance whilst requiring less power and lower fabrication costs. Dr Arianna Filoramo, a researcher at CEA-Saclay and **SATURN** project partner, explained how current research is looking into areas such as the fabrication and characterisation of low dimensional materials such as nanowires, nanotubes and nanodots; new methods of fabricating nanodevices such as self-assembly and molecular lego; as well as new architecture paradigms for nanodevices.

A third strand was nano-electro-mechanical systems (NEMS). Said Professor Jürgen Brugger of Ecole Polytechnique Fédérale de Lausanne (EPFL): "I would like to emphasise the 'm' in nanoelectro-mechanical systems. We are really focussing on the mechanical aspects of nanodevices." The identified challenges being tackled included nanoscale mechanics, fabrication techniques for NEMS elements, detection methods and interfacing of NEMS.

The broad spectrum of discussions that took place at the NID Workshop served to show that the semiconductor industry is entering an exciting, if uncertain, period. The expected physical challenges of advancing CMOS technology is creating a flurry of activity which is leading to a wide range of potential technical successors. Technology fragmentation means there will be a tremendous opportunity for the industry to differentiate and so add value, supported by researchers such as those at the NID Workshop.

Contact:

#### Dr Patrick Van-Hove

DG Information Society and Media- F1 (BU33 3/11) European Commission (Belgium) Email: **patrick.van-hove@cec.eu.int**

#### Legal notice:

© European Communities, 2003 Reproduction is authorised provided the source is acknowledged

The content is prepared by the IST Results service and offers news and views on innovations, emerging from EU-funded Information Society Research. The views expressed in the articles have not been adopted or in any way approved by the European Commission and should not be relied upon as a statement of the Commission or the Information Society DG.

#### NID Working Group on Mono-Molecular Electronics

Coordinators: C. Joachim and G. Meyer 3rd meeting, February the 1st, 2005

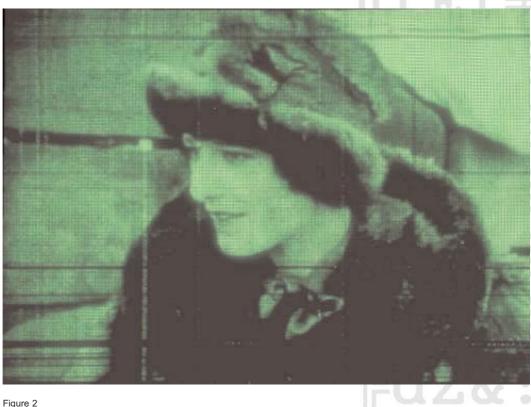

This 3rd meeting focussed on architecture problem. The central question on the stage was: for molecular electronics, will it be necessary to remain at the single molecule = one device challenge or do we need to explore more how a single molecule, of course more complex can perform more than a simple amplification, rectifier or rectifier action. Of course, there are a lot of architectural options to be explored ranging from forcing the molecule to have the topology of a miniaturized electronic circuit to the use of quantum intramolecular non-stationnary time evolution to perform a logic function. The important point here is not to be restricted to a given technology but to provide new ways to design an ultra-small piece of material to compute.

The third presentation was given by C. Joachim from the Nanoscience group of CEMES/CNRS (Toulouse). He had presented the principle of a new intramolecular logic gate design called Quantum Hamiltonian Computing. Using an intramolecular single electron transfer process, it was shown how computing inside a quantum system can be performed using the time evolution driven by the preparation of the system in a non-stationary state. The molecule Hamiltonian is separated in three parts: the input, calculation, and output parts. Two optimisation procedures were described in order to design an efficient mono-electronics level structure for molecular logic gates. An XOR gate and a halfadder using six electronic quantum levels were presented. A dinitro[1,3]anthracene molecule was described, performing an fi adder logic function with no resemblance to the topology of an electronic circuit performing the same function. The logic function is obtained by the control of the molecule quantum trajectory in its p molecular orbitals electronic quantum state space by changing the conformation of the nitro groups, starting from an initial non-stationary state independent of the input configuration. Questions arise from the audience about the practical way to program the input status and to read out the results.

| Agenda        |                                                                                            |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| 15:00 - 15:15 | C. Joachim: M2e Presentation, Scope and Goals                                              |  |  |  |  |

| 15:15 – 15:30 | D.Guedj: Atom-Based Technologies?                                                          |  |  |  |  |

| 15:30 - 16:00 | F. Remacle: Towards Molecular Logic Machines Using Inter- and Intra-Moelcular<br>Dynamics  |  |  |  |  |

| 16:00 - 16:30 | C. Joachim: What Kind of Mono-Molecular Electronics: Architecture, Technology & Chemistry? |  |  |  |  |

| 16:30 - 17:00 | Discussion & Conclusions                                                                   |  |  |  |  |