# CArbon Nanotube Devices for Integrated Circuit Engineering

ISIT

# **Project outline**

### Aims:

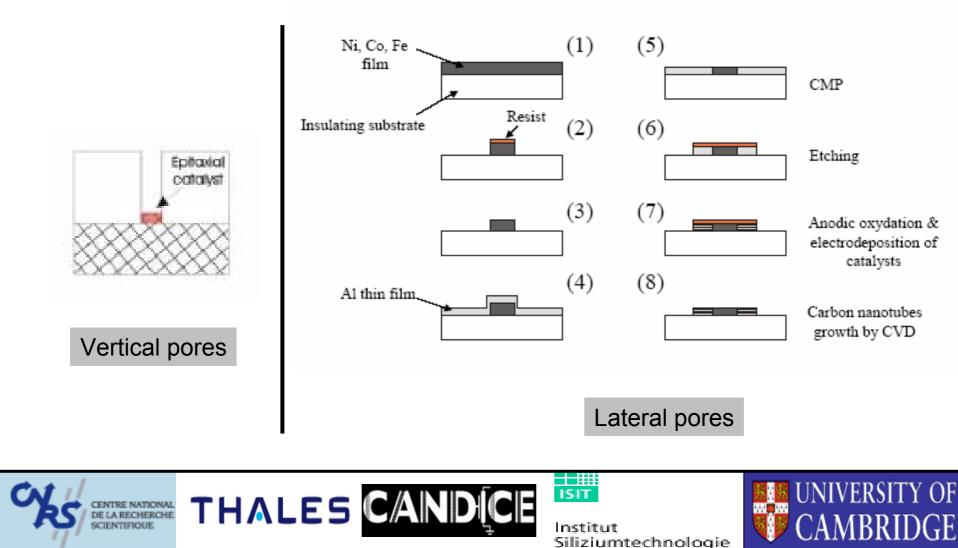

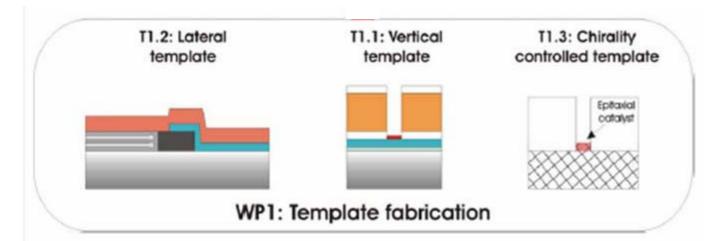

- 1- Organisation of CNTs in templates

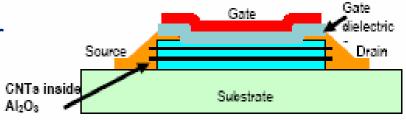

- Vertical templates: top down process

- Lateral templates: rather bottom up

- 2- Chirality control?

- 2- Cambridge University

- 3- Thales Research & Technology

### 4- Frauhofer ISiT

Micro-machined SiO<sub>2</sub>/poly-Si deposits

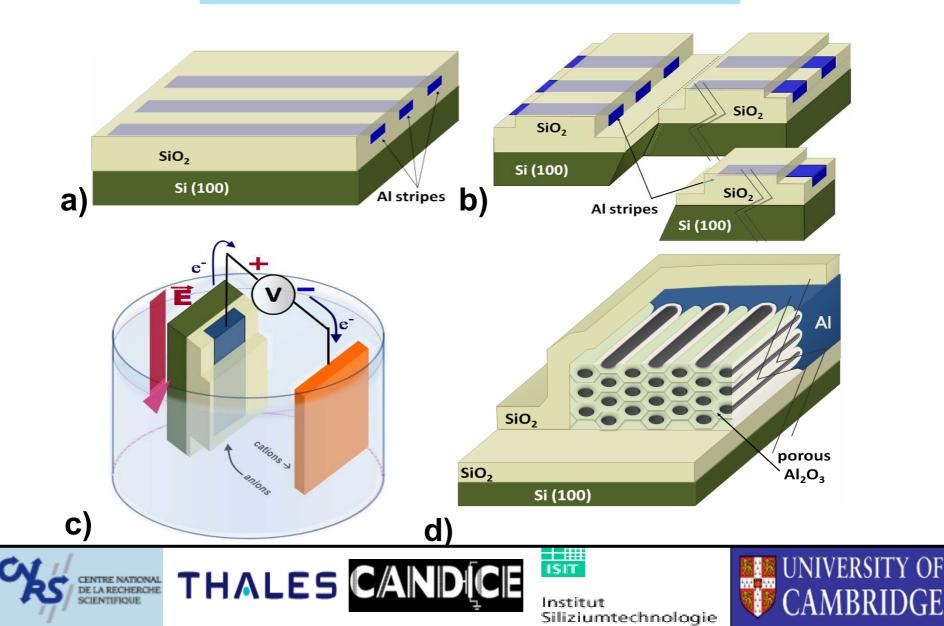

#### Lateral anodic alumina

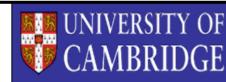

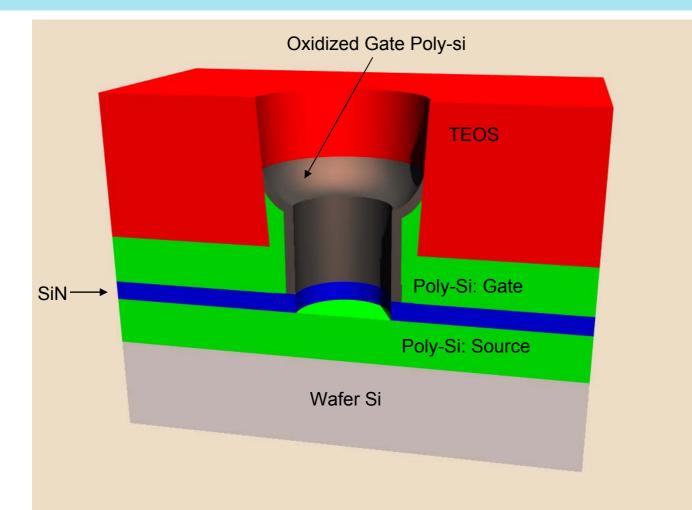

### **Process outline- Vertical templates**

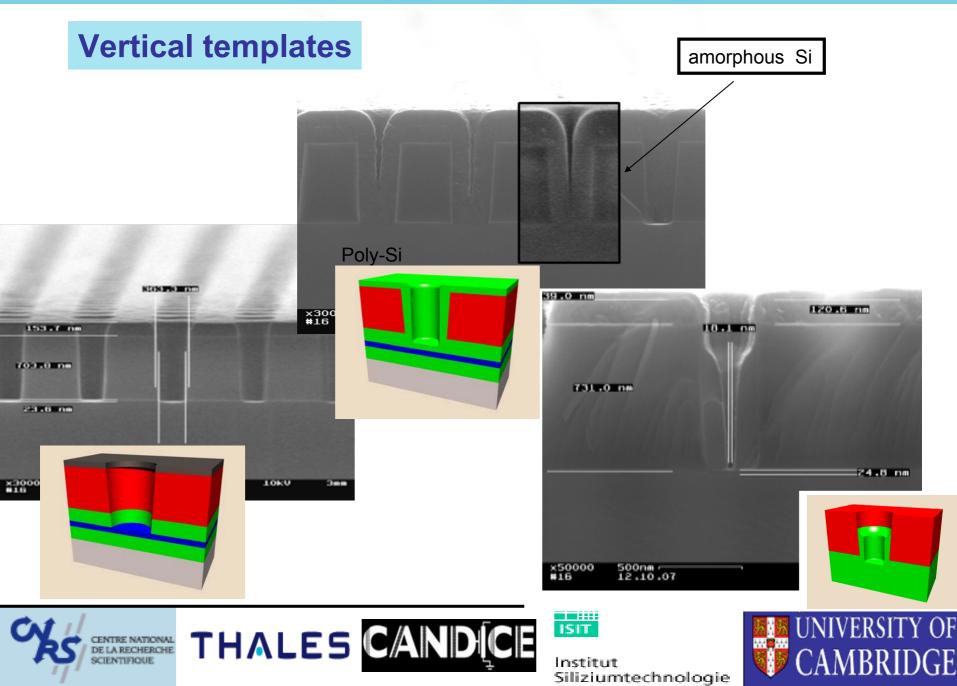

## **Vertical templates**

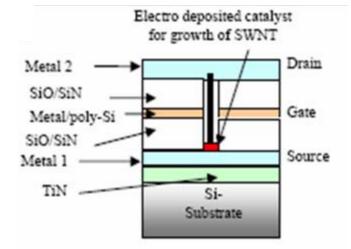

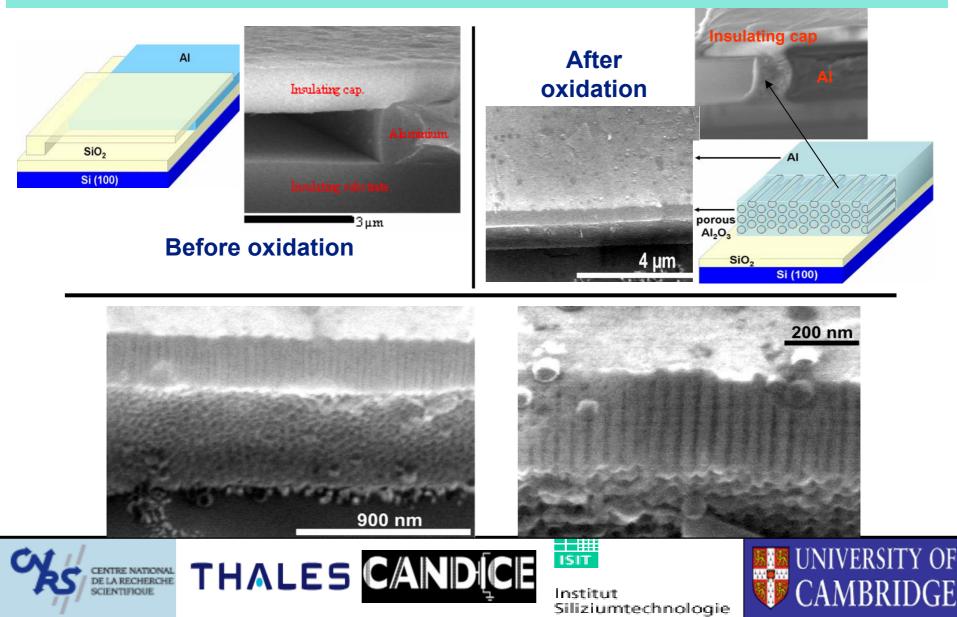

### **Process outline- Lateral templates**

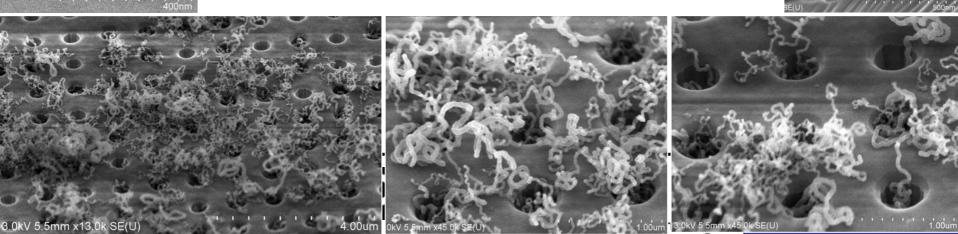

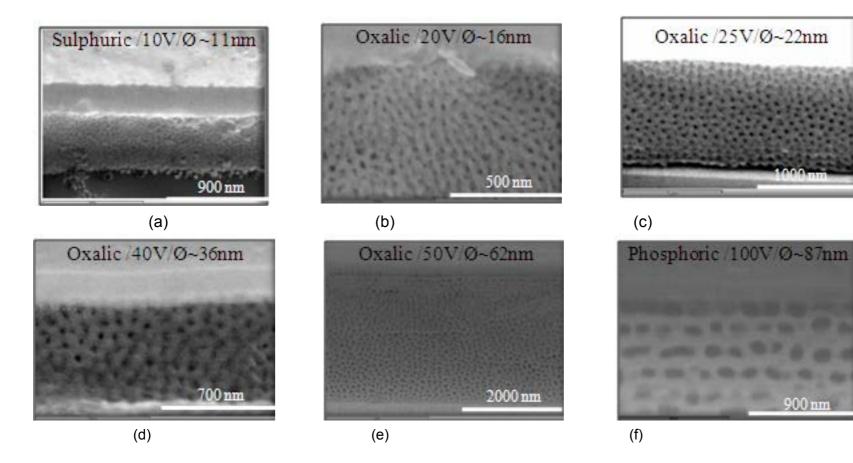

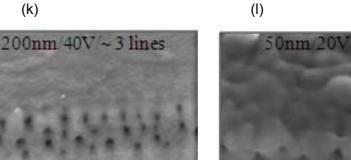

### **Results – different pore diameters**

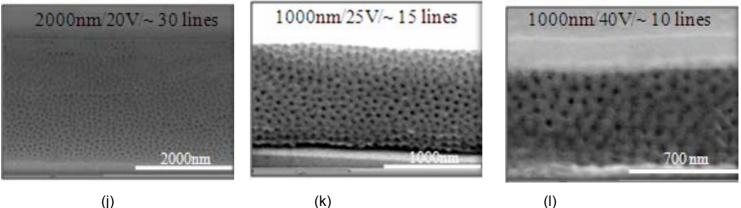

### **Results – different arrays**

(g)

(i)

400nm

as grown

after sonication

broken CNTs

500nm

500nm

1.00um 1.5kV 2.4mm x110k SE(U.LA5)

3.0kV 2.9mm x35.0k

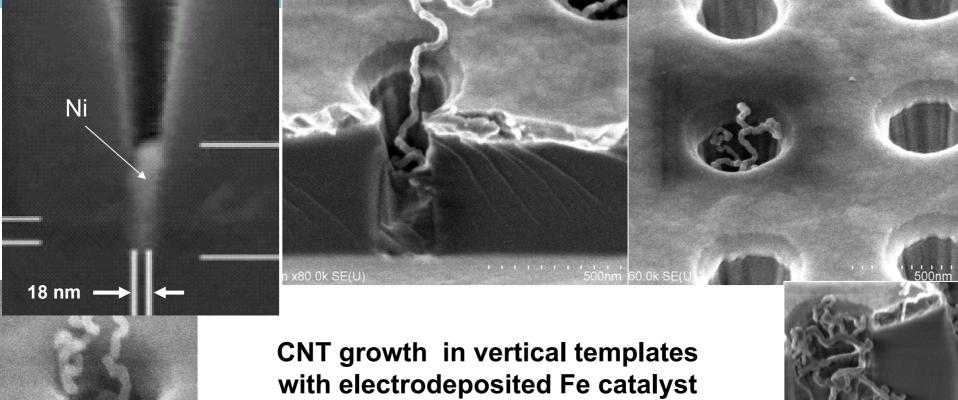

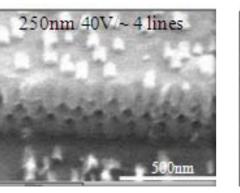

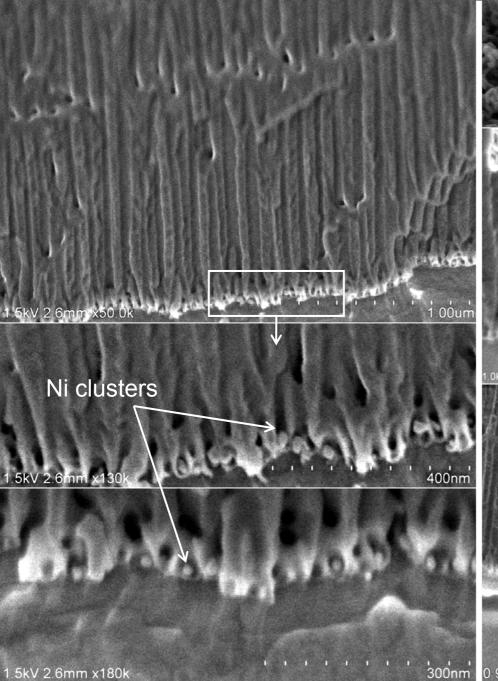

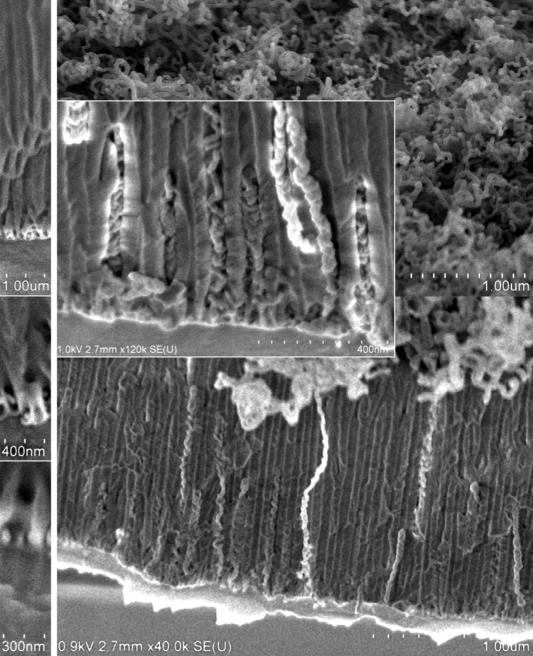

### CNT growth in vertical Al<sub>2</sub>0<sub>3</sub> membranes

0 9k/ 2 4mm x80 0k SE(U)

500nm 0 9kV 2 4mm x110k SE(U)

High aspect ratio PAA template with electrodeposited Ni catalyst and the subsequent CM

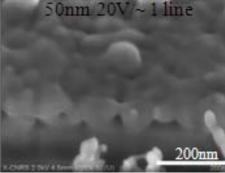

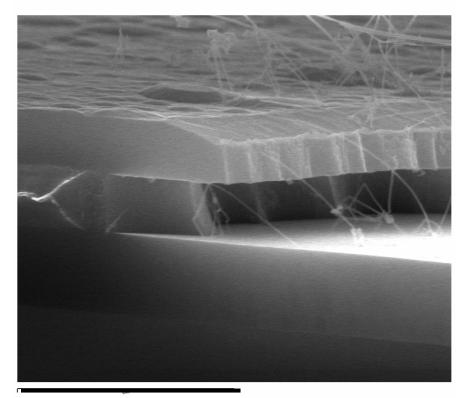

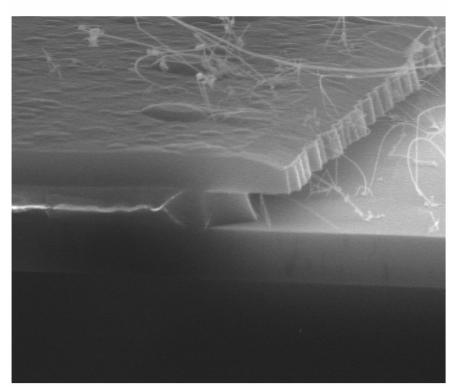

# **Growth in lateral membranes: first trials (1)**

# Growth in lateral membranes: first trials (2)

# Conclusions

- Templates fabricated according to expectations

- CVD growth inside templates

- OK for vertical FET structure

- Needs to be calibrated for lateral growth

- Vertical devices will be realised in the next few months

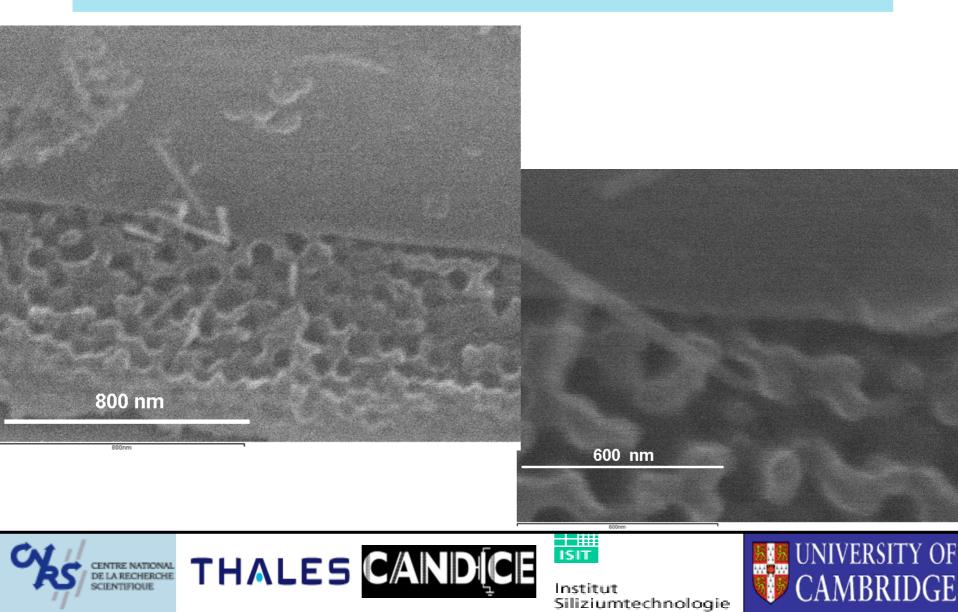

## SEM observation of lateral anodic alumina templates

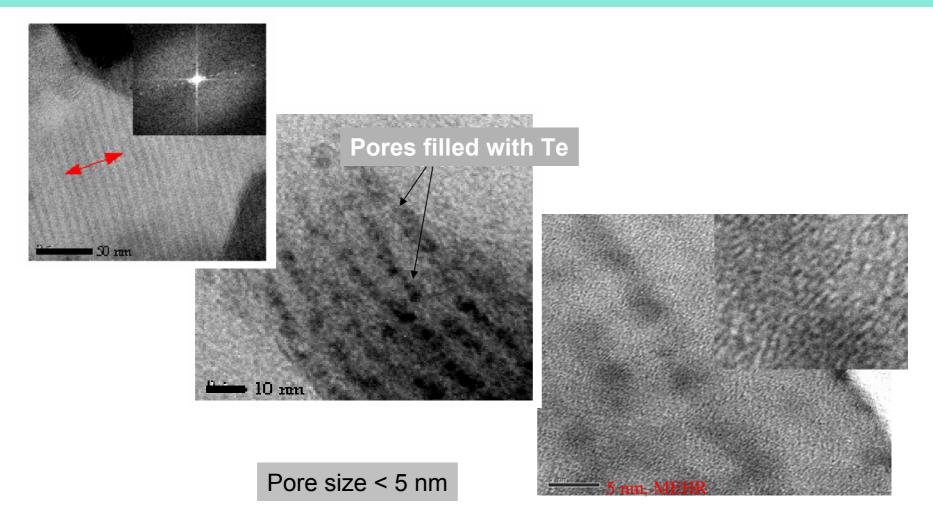

# TEM observation of lateral anodic alumina templates

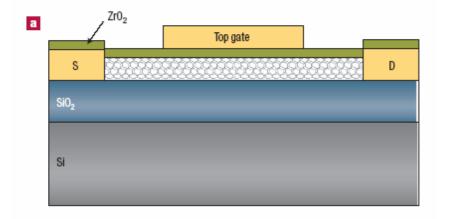

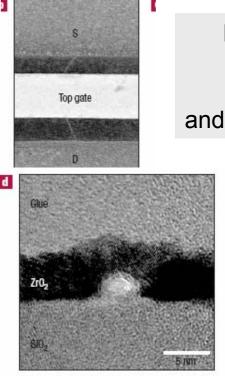

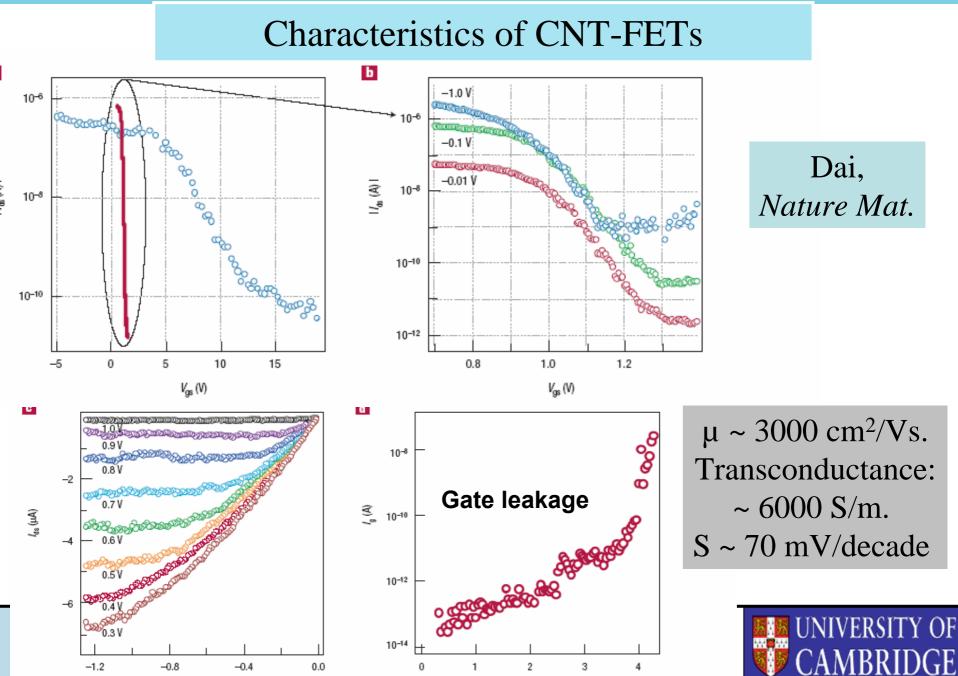

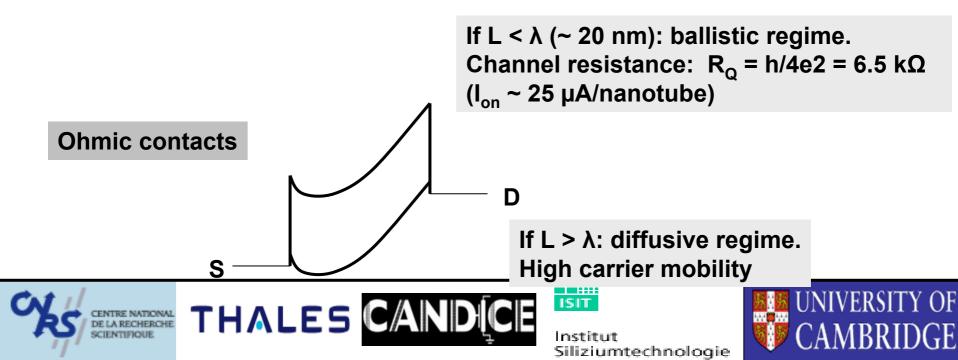

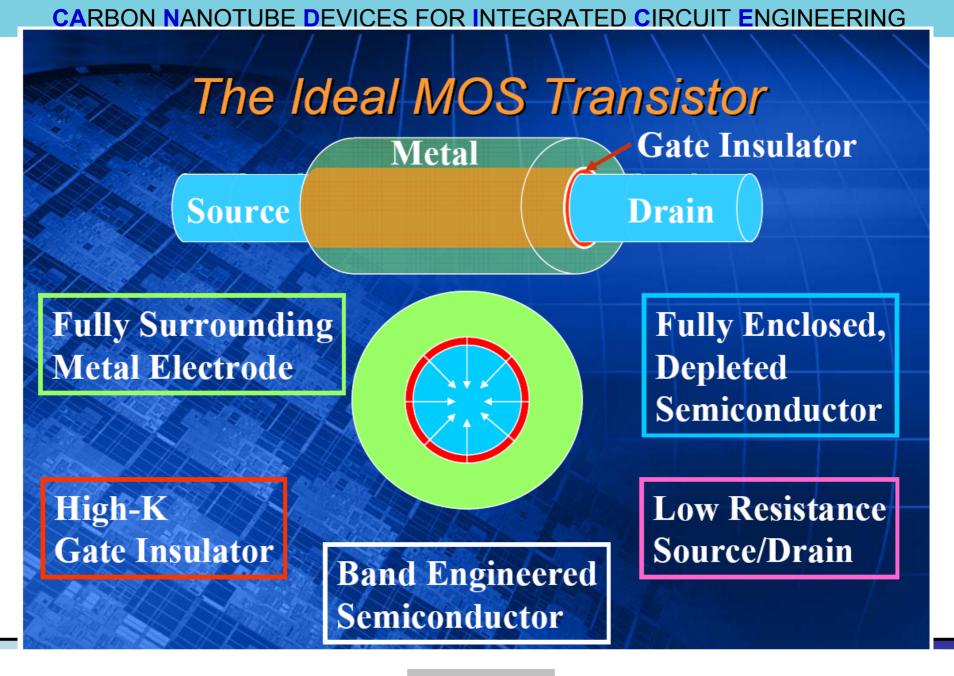

# CNT-Field Effect Transistor (FET)

$\mu \sim 3000 \text{ cm}^2/\text{Vs.}$ Transconductance: ~ 6000 S/m. S ~ 70 mV/decade

HfO<sub>2</sub>, ZrO<sub>2</sub>  $\sim$  3nm. Top gate and top contacts.

Dai's group, *Nature Mat.*, 2002 Avouris' group, *Proc. IEEE*, 2003

## Comparison between CNT-FETs and ultimate MOSFETs

| Comparison between CNT FET and ultra-scaled planar Si FET |                     |                              |  |  |  |  |  |  |

|-----------------------------------------------------------|---------------------|------------------------------|--|--|--|--|--|--|

| Transistor parameter                                      | p-Type<br>CNFET [7] | p-Type silicon<br>MOSFET [8] |  |  |  |  |  |  |

| Physical gate length (nm)                                 | 260                 | 15                           |  |  |  |  |  |  |

| Gate oxide thickness (nm)                                 | 15                  | 1.4                          |  |  |  |  |  |  |

| Threshold voltage $V_t$ (V)                               | 0.5                 | ∼−0.1                        |  |  |  |  |  |  |

| On-state current I <sub>ON</sub> (µA/µm)                  | 2100                | 265                          |  |  |  |  |  |  |

| Off-state kakage I <sub>OFF</sub> (nA/µm)                 | 150                 | <500                         |  |  |  |  |  |  |

| Subthreshold slope (mV/dec)                               | 130                 | ~100                         |  |  |  |  |  |  |

| Transconductance (µS/µm)                                  | 2321                | 975                          |  |  |  |  |  |  |

Yu & Meyyappan, Solid St. Electr. 2006

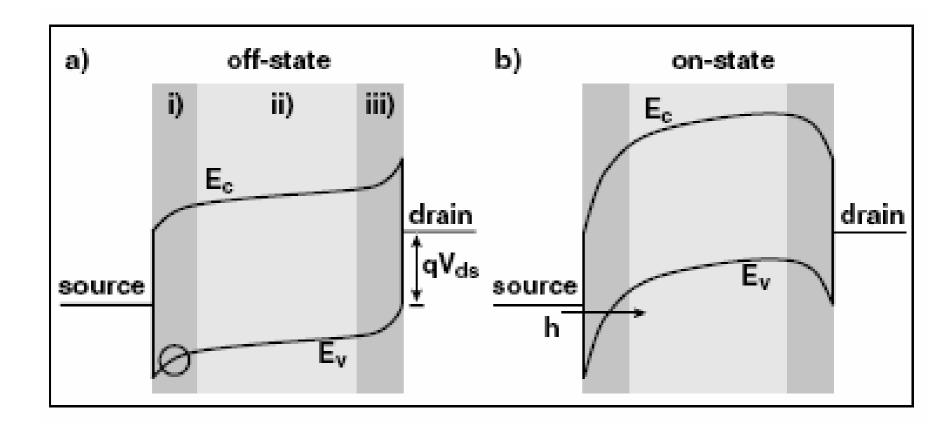

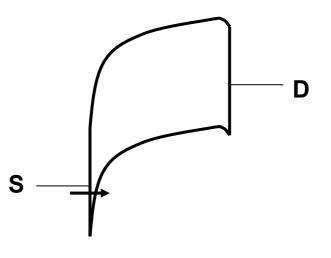

The most common situation for CNT-FETs: Schottky contacts at Source and Drain

# Summary for CNT-FETs

General situation: Current limited by the contact Schottky barriers

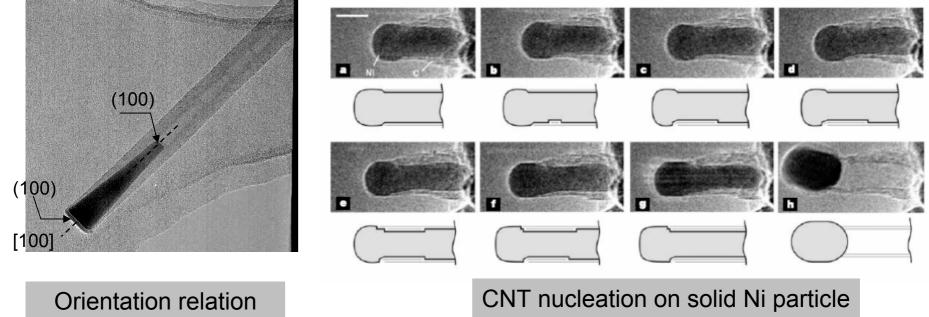

# Chirality control?

between a Fe catalyst particle and the CNT (after growth)

T~ 480°C

ISIT

## « Epitaxial » catalyst

## WP structure (1)

THALES CANDICE

### WP structure (2)

THALES CANDICE

# Project bar chart

|                         |                                                   |    |    | Partner mm |    |     |       | Duration |   |  |       |  |  |  |       |  |  |  |

|-------------------------|---------------------------------------------------|----|----|------------|----|-----|-------|----------|---|--|-------|--|--|--|-------|--|--|--|

| Workpackage description |                                                   | 1  | ,  | 3          | 4  | т   | Year1 |          |   |  | Year2 |  |  |  | Year3 |  |  |  |

|                         |                                                   | 1  | -  | 3          | 4  | 1   |       |          |   |  |       |  |  |  |       |  |  |  |

| WP1                     | Template fabrication                              |    |    |            |    |     |       |          |   |  |       |  |  |  |       |  |  |  |

| T1.1                    | Vertical templates                                |    |    |            | 15 | 15  |       |          |   |  |       |  |  |  |       |  |  |  |

| T1.2                    | Lateral templates                                 | 12 |    | 3          |    | 15  |       |          |   |  |       |  |  |  |       |  |  |  |

| T1.3                    | Templates for chirality control                   | 5  |    | 4          |    | 9   |       |          |   |  |       |  |  |  |       |  |  |  |

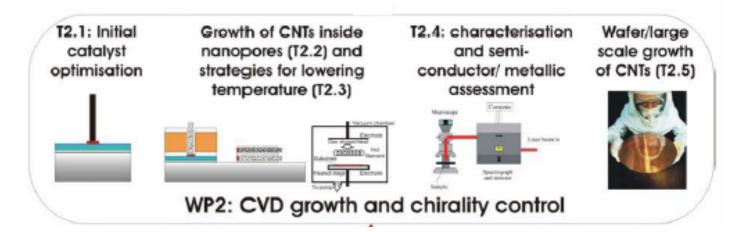

| WP2                     | CVD growth and chirality control                  |    |    |            |    |     |       |          |   |  |       |  |  |  |       |  |  |  |

| T2.1                    | Initial catalyst optimisation                     |    | 10 | 3          |    | 13  | I     |          |   |  |       |  |  |  |       |  |  |  |

| T2.2                    | Growth of carbon nanotubes inside nanopores       | 5  | 12 | 1          |    | 18  |       |          |   |  |       |  |  |  |       |  |  |  |

| T2.3                    | Lowering growth temperature for chirality control | 12 | 10 |            |    | 22  |       |          |   |  |       |  |  |  |       |  |  |  |

| T2.4                    | Charact. and semiconductor/metallic assessment    | 4  | 9  | 3          |    | 16  |       |          |   |  |       |  |  |  |       |  |  |  |

| T2.5                    | Wafer/large scale growth of carbon nanotubes      |    | 7  |            |    | 7   |       |          |   |  |       |  |  |  |       |  |  |  |

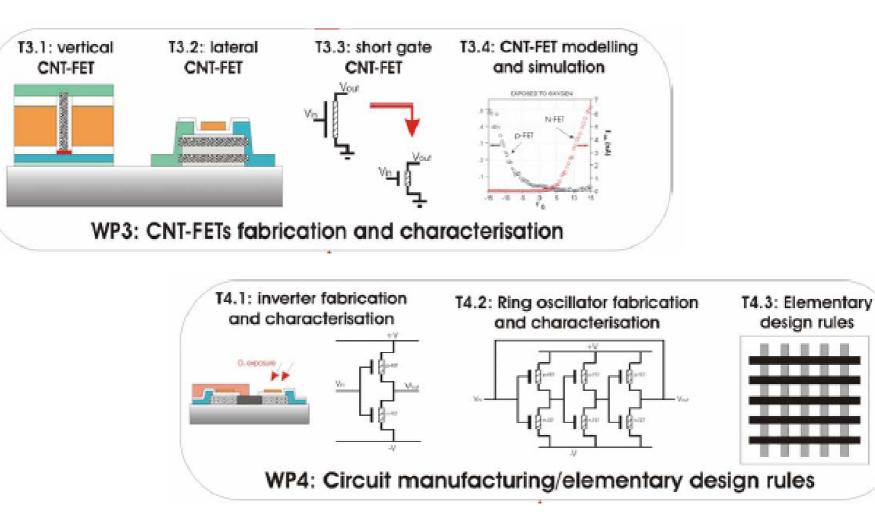

| WP3                     | CNT-FETs fabrication and characterisations        |    |    |            |    |     |       |          |   |  |       |  |  |  |       |  |  |  |

| T3.1                    | Vertical CNT-FET                                  | 1  |    |            | 9  | 10  |       |          |   |  |       |  |  |  |       |  |  |  |

| T3.2                    | Lateral CNT-FET                                   | 6  |    | 6          |    | 12  |       |          |   |  |       |  |  |  |       |  |  |  |

| T3.3                    | Short gate CNT-FETs                               |    | 13 |            | 5  | 18  |       |          |   |  |       |  |  |  |       |  |  |  |

| T3.4                    | CNT-FET modelling and simulation                  | 10 |    |            | 3  | 13  |       |          |   |  |       |  |  |  |       |  |  |  |

| WP4                     | Circuit manufacturing/Elementary design rules     |    |    |            |    |     |       |          |   |  |       |  |  |  |       |  |  |  |

| T4.1                    | Inverter fabrication and characterisation         | 6  | 6  | 2          | 1  | 15  |       |          |   |  |       |  |  |  |       |  |  |  |

| T4.2                    | Ring oscillator fabrication and characterisation  | 6  | 6  | 2          | 1  | 15  |       |          |   |  |       |  |  |  |       |  |  |  |

| T4.3                    | Elementary design rules                           | 1  |    |            | 1  | 2   |       |          |   |  |       |  |  |  |       |  |  |  |

| T4.4                    | Assessment of CMOS compatibility                  | 1  | 1  | 1          | 1  | 4   |       |          |   |  |       |  |  |  |       |  |  |  |

| WP5                     | Project management                                | 6  | 1  | 1          | 1  | 9   |       |          |   |  |       |  |  |  |       |  |  |  |

|                         | Totals                                            | 75 | 75 | 26         | 37 | 213 |       | _        | _ |  |       |  |  |  |       |  |  |  |

THALES CANDICE Institut Siliziumtechnologie

ISIT

We have been working on CNTs as well as on Si nanowires

### Question: Can we include NWs in the project as well?

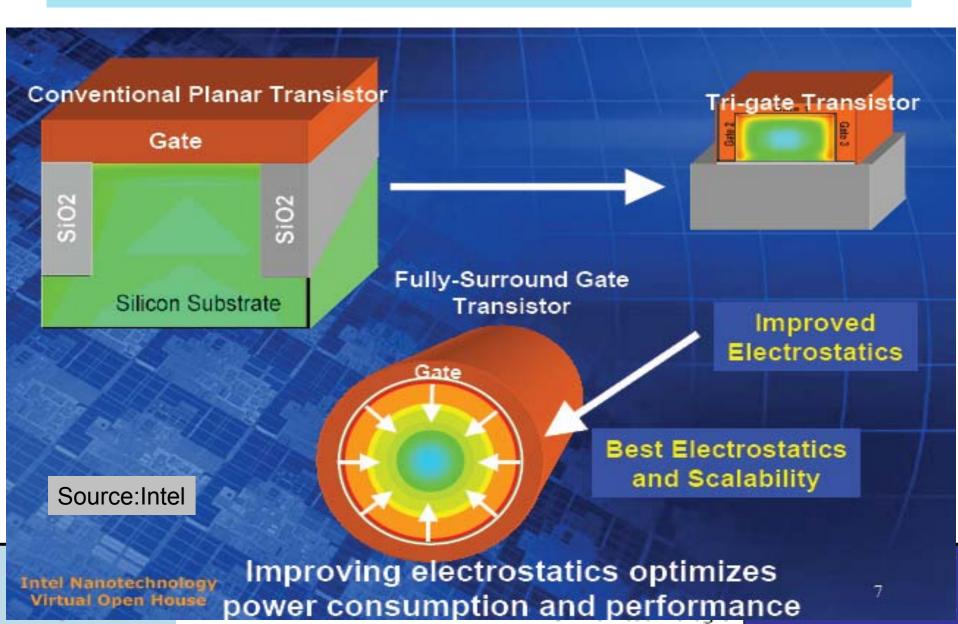

## Evolution of device technology

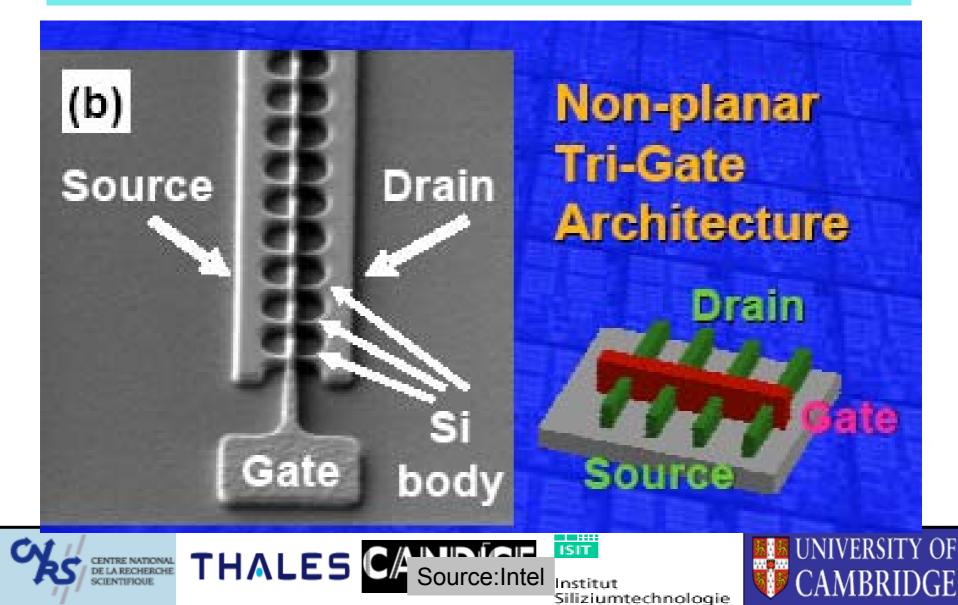

## Trigate/multichannel transistors

Source:Intel

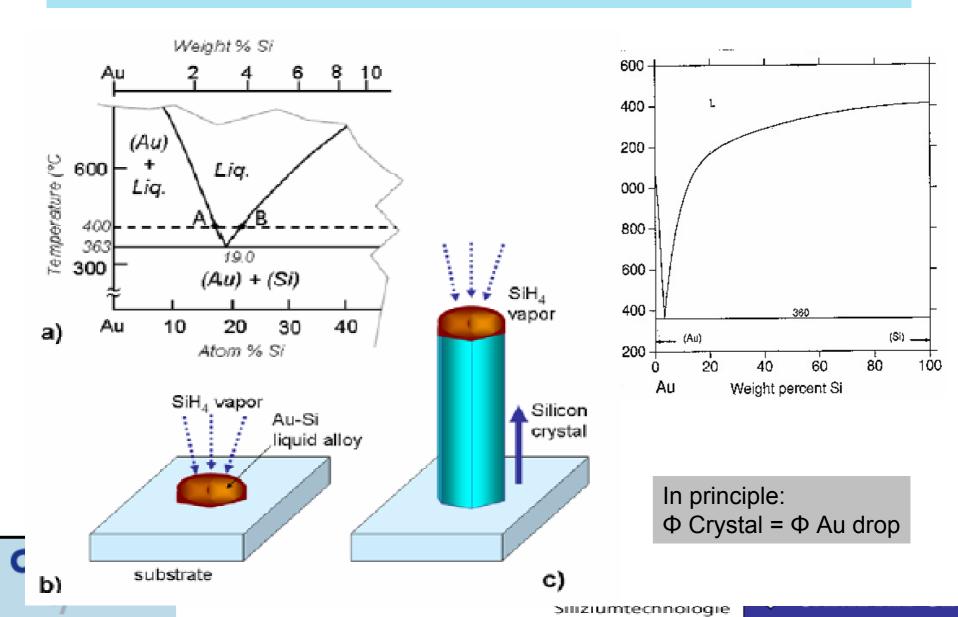

### Principle of the VLS Growth method

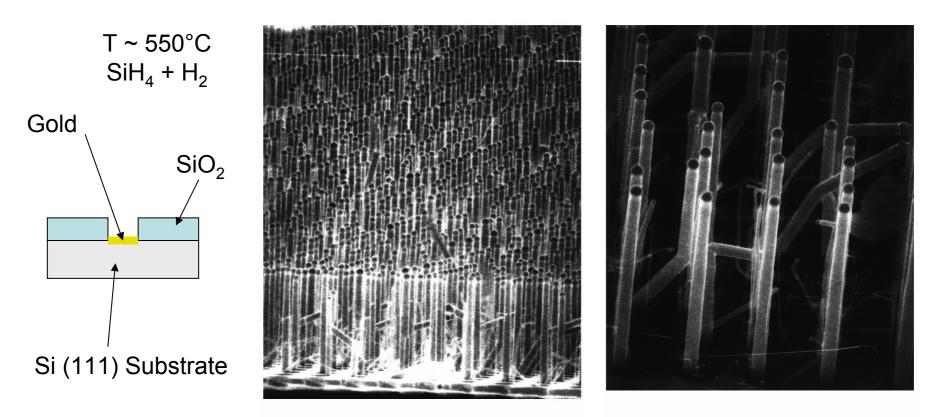

### VLS growth of Si whisker arrays

1<u>5</u> μm

7.5 µm

THALES CANDICE

Institut Siliziumtechnologie

ISIT