## Beyond silicon electronics-FETs with nanostructured graphene channels with high on-off ratio and high-mobility

## M.Dragoman<sup>1</sup>

A.Dinescu<sup>1</sup>, and D.Dragoman<sup>2,3</sup>

<sup>1</sup>National Institute for Research and Development in Microtechnology (IMT), P.O. Box 38-160, 023573 Bucharest, Romania,

<sup>2</sup>Univ. Bucharest, Physics Faculty, P.O. Box MG-11, 077125 Bucharest, Romania <sup>3</sup>Academy of Romanian Scientists, Splaiul Independentei 54, 050094 Bucharest, Romania

## mircea.dragoman@imt.ro

We have demonstrated recently (see [1] and the references herein) that graphene ordered arrays of nanoholes of 100 nm in diameter and with a periodicity of 100 nm can be patterned on a wafer scale by elithography. Nanopatterned graphene is used as channel with a length of 20 µm in graphene FETs, opening a bandgap of 0.2 eV. As a result an on/off ratio of at least 2x 10<sup>3</sup> at room temperature is obtained. Our results show a maximum transconductance of about 1 mS at a gate voltage of -3 V, a mobility of 2200 cm<sup>2</sup>/V·s satisfying the condition according to which a FET based on 2D material is a digital switch [2] The obtained mobility is higher than in Si and is higher than in the majority two-dimensional transition metal dichalcogenides, which are the most widespread atomically thin materials nowadays. In addition, the built-in electric field due to localized edge states at the holes increases with orders of magnitude photoresponse of nanopatterned GFETs. We have scaled down the above FET to see if we can get better performances. In this respect, we have made batch fabrication

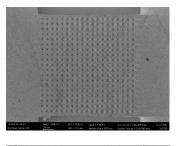

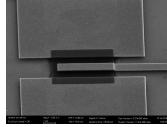

nanopatterned graphene FETs with much smaller holes (20-25 nm in diameter) and much smaller channel lengths i.e. 1  $\mu$ m, 2  $\mu$ , 4  $\mu$  and 8  $\mu$ m (see Fig.1) using as gate dielectric HSQ with a thickness of 40 nm. We have observed that while the transconductance is in the range 0.7-0.9 mS the mobility is reaching even 10 000 cm²/Vs preserving an on-off ratio of 10³. In this respect, nanopatterned graphene FETs could be comparable in the near future with high performance transistors based on GaAs and GaN.

Fig. 1 The nanopatterne d graphene channel and the GFET top view.

## References

[1] M. Dragoman, A. Dinescu, and D. Dragoman, Room temperature nanostructured graphene transistor with high on/off ratio, Nanotechnology 28, 015201 (2017).

[2] F. Schwierz, J. Pezoldt, and R. Granzner, Two-dimensional materials and their prospects in transistor electronics, Nanoscale 7, 8261 (2015).