## Carbon based resistive random access memories with graphene electrodes

A. K. Ott, C. Dou, U. Sassi, I. Goykhman, A. C. Ferrari\*

Cambridge Graphene Centre, 9 JJ Thomson Avenue, Cambridge CB3 0FA, UK \*acf26@hermes.cam.ac.uk

## Abstract

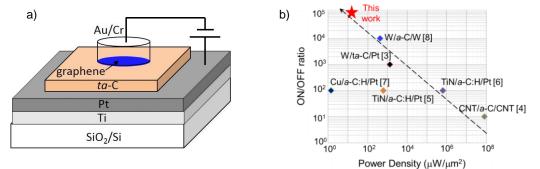

There are two main types of semiconductor random access memory (RAM), static RAM (SRAM) and dynamic RAM (DRAM). Both are volatile, i.e. they lose the stored information when power is off [1]. SRAMs are currently used in central processing unit (CPU) registers due to their fast write/erase times~0.3ns[1]. Scaling is a problem, as SRAMs are made of six transistors resulting in rather large cells[1]. DRAMs store information in an integrated capacitor[1]. They require periodic refreshing to regenerate the data, due to their slow discharge as result of leakage currents[1], resulting in increased power consumption[1]. FLASH memories are non-volatile and rely on electrical charge stored by a floating gate, making scaling below 16nm difficult[1]. Due to these problems, there is an urgent need for alternatives. Resistive RAMs (RRAMs) are a new type of non-volatile memory based on a change in resistance initiated by electric fields[1-3]. Tetrahedral amorphous carbon (ta-C) shows reversible, nonvolatile resistive switching[2,3] offering a route for future generation high-performance, cost-effective and environmentally friendly data storage[2-8]. RRAM elements are integrated in circuits as crossbar arrays, i.e. the top electrode is rotated at 90 degrees with respect to the bottom electrode[9]. However, sneak or leakage currents are a major issue causing read errors[9,10]. Having a high ON/OFF ratio is a key requirement for RRAMs[10] to achieve the smallest theoretical cell size of 4F<sup>2</sup>, where F is the minimum feature size, by eliminating the access transistors[10,11]. Here we integrate graphene/metal electrodes in ta-C-based RRAMs, Fig.1a). Our devices show large ON/OFF ratios ~4x10<sup>5</sup> and low power density of 14µW/µm<sup>2</sup>, with no requirement of high voltage to first form a conductive filament, and polarity-independent operation, Fig.1b). The ON/OFF ratio is 10 times higher than in devices based on conventional metal electrodes[2-8], with no increase of operational voltage and set current. This is due to the suppressed tunneling or leakage current induced by the low density of states of graphene near the Dirac point. These results show that graphene is an excellent candidate to tackle the biggest disadvantage of crossbar arrays and paves the way for replacing conventional RRAM architectures.

## References

- [1] D. S. Jeong et al., Rep. Prog. Phys., 75 (2012) 076502.

- [2] D. Fu et al., IEEE Electron Device Lett., **32** (2011) 803.

- [3] J. Xu et al., Carbon, 75 (2014) 255.

- [4] Y. Chai et al., IEDM Tech. Dig. (2010) 214.

- [5] L. Dellmann et al., Proc. of 43rd ESSDERC, (2013) 268.

- [6] Y. J. Chen et al., Nanoscale Research Lett., 9 (2014) 52.

- [7] F. Zhuge et al., Appl. Phys. Lett. 96 (2010) 163505.

- [8] F. Kreupl et al., IEDM Tech. Dig. (2008).

- [9] E. Linn et al, Nat. Mat. 9 (2010) 403.

- [10] L. Zhang IEEE Electron Device Lett. 36 (2015) 570.

- [11] M. Shevpoor, Proc. of 34<sup>th</sup> IEEE ICCD, (2015)

## Figures

**Fig 1:** a) Schematic of device structure with graphene/metal electrode. b) Comparison of ON/OFF ratio of a-C based memory devices versus power density.