## A technology for graphene based millimeter wave integrated circuits

G. Deligeorgis<sup>1\*</sup>, A. Ziaei<sup>2</sup>, V. Prudkovskiy<sup>1,3</sup>, F. lacovella<sup>1,3</sup>, S. Xavier<sup>2</sup>, R. Yakimova<sup>4</sup>, M.Modreanu<sup>5</sup> and G. Konstantinidis<sup>1</sup>

<sup>1</sup>FORTH – IESL Microelectornics Research Group, P.O.Box 1583 Irakleio, Crete, Greece <sup>2</sup>Thales Research and Technology, Palaiseau, France <sup>3</sup>University of Crete, Physics Department, 70013 Irakleio, Greece <sup>4</sup>Department of Physics, Chemistry, and Biology, Linköping University, S-581 83 Linköping, Sweden <sup>5</sup>Tyndall National Institute-UCC, Lee Maltings, Dyke Parade, Cork, Ireland deligeo@physics.uoc.gr

## Abstract (Arial 10)

Graphene and other two dimensional materials have been at the forefront of electronics research during the past 10 years. Their extreme form factor as well as their unique properties have provided a new platform to develop devices with novel functionality <sup>1</sup>. On the other hand 2D materials are inherently sensitive to their surrounding making processing complex circuits a challenge<sup>2,3</sup>.

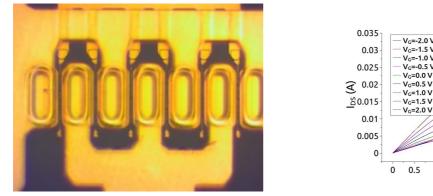

We will discuss integration of graphene based devices into complex high frequency circuits including detection and signal amplification in the GHz frequency range. We will present our established technology on graphene FETs (field effect transistors) operating in the microwave frequency range. Values of transconductance as high as 200mS/mm stemming from optimization of contact resistance to values below 200 Ohms/µm <sup>4,5</sup> and top gated structures using HfO<sub>2</sub> below 10nm in a complete MMIC compatible fabrication technology that includes passive components will be detailed. We plan to discuss this technology in the frame work of fabricating graphene based monolithically integrated low noise amplifier (LNA) circuits on graphene on SiC as this substrate provides the best heat dissipating properties compared to other alternatives.

## References

<sup>1</sup>G. Deligeorgis, F. Coccetti, G. Konstantinidis, and R. Plana, Appl. Phys. Lett. **101**, 013502 (2012).

<sup>2</sup> F. Schwierz, Nat Nano advance online publication, (2010).

<sup>3</sup> F. Schwierz, Proc. IEEE **101**, 1567 (2013).

<sup>4</sup> B.-C. Huang, M. Zhang, Y. Wang, and J. Woo, Appl. Phys. Lett. **99**, 032107 (2011).

<sup>5</sup> A.D. Franklin, S.-J. Han, A.A. Bol, and V. Perebeinos, IEEE Electron Device Lett. **33**, 17 (2012).

## **Figures**

Figure 1: Image of a multi-finger FET device optimized for GHz operation (left) and typical *output characteristics (right)*

1.5

1

2.5 3

2 V<sub>DS</sub> (V)